Part Number: DS90UB960-Q1

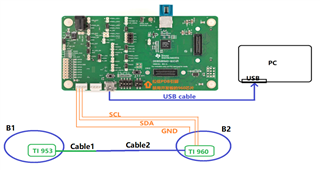

We have the boar B1 and B2. B1 has TI953 and B2 has TI960.

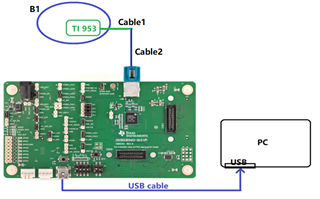

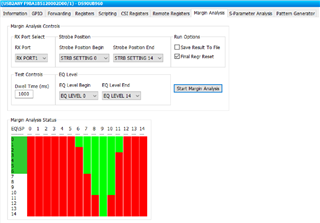

We use the DS90UB960-Q1 EVM board to test the Margin. Here is a comparative experiment.

1.Wnen connect B1 and EVM board, the Margin test is ok.

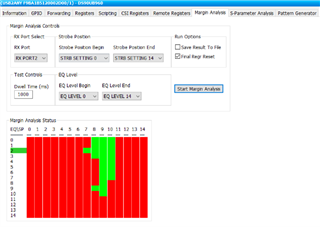

2.When connect B1 and B2, the Margin test is failed.

What can we get from the above test?

According to my understanding, the purpose of margin test is to verify the stability of the physical link between ti953 and ti960. If the margin test fails, it indicates that the connection between ti953 and ti960 is unstable, which will lead to a series of problems such as lock loss, data transmission error and so on.

I wonder if there is any problem with my understanding? Please check it.