Part Number: DS90UB933-Q1

hi Team

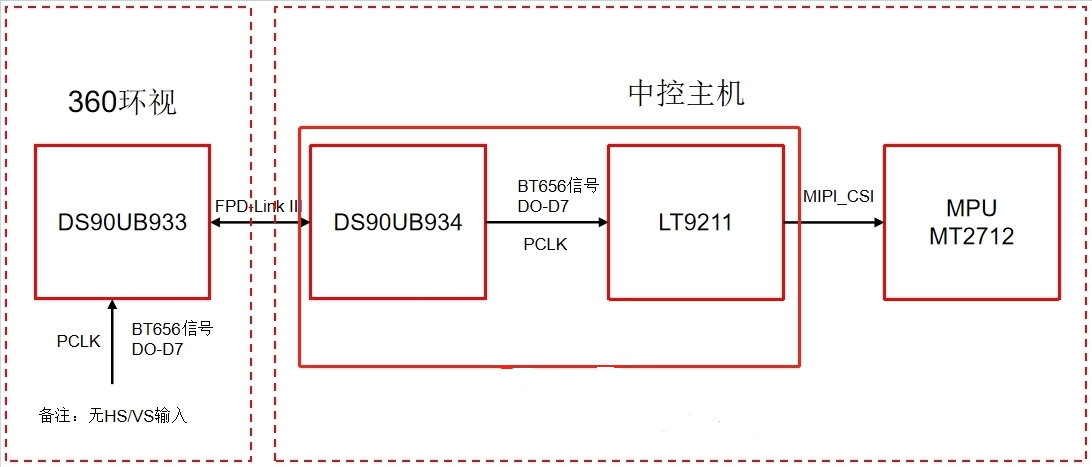

At present, it is found in the actual boarding test that the control screen will flash on the 360 look around interface (see Annex),

one At present, the frequency of PCLK is set to 95MHz, which is close to the limit value of 100MHz required by 933 / 934. Is it possible that this PCLK is too high or for other reasons? Can you help analyze it;

two Is there any instrument that can monitor whether the video picture of 934 output bt656 signal is abnormal;