Hello team,

I have some questions regarding TCAN1146-Q1 input capacitance.

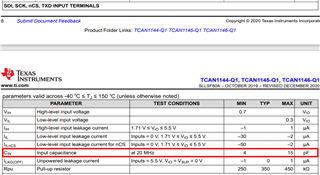

- In the datasheet the input capacitance for TXD is stated as max. 15pF at 20MHz (see below screenshot). Why is 20MHz the test condition?

- What is the input capacitance of TXD at 10MHz or 5MHz, wouldn’t this test condition be closer to application at max. data-rate at 5Mbps?

Thank you,

Muwei Zheng