Dear Representative,

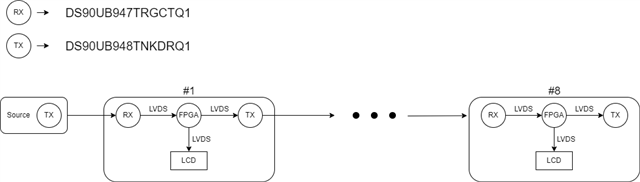

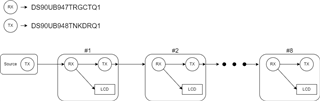

We are working on project which may consist of chain from x8 series links. Each link is TX+RX. where: TX is DS90UB947-Q and RX is DS90UB948-Q, here I attached simple diagram for understanding:

Can you please advice, will this configuration work:

1. from I2C bus point of view?

2. from I2S bus point of view?

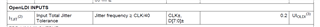

Because in datasheet noted, what the maximum possible configuration is(see image below):

Thank you!

Looking forward your answer!

Sergej.