Hello,

We have connected an ethernet phy DP83867IRPAP device to our custom silicon on our in-house developed board, and the bootstrap is set to configure the device in RGMII mode, Autoneg enabled. In RGMII mode 1G we could see the device responds properly, the link is set up, and with Autoneg enabled, we could see the phy configures itself into either 100Mpbs or 1Gbps based on the type of connected peer.

Unfortunately, we are unable to transmit/receive ICMP packets (ping) from our target to the host for 100/1000 speed.

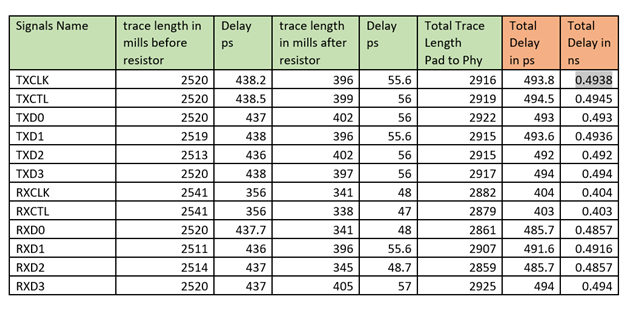

-Delay control register is set to 0x77. i.e 2ns for both TX and RX.

-In the U-Boot environment (2020.07-rc3). When we trigger ping from target to Host PC we don't receive any reply.

We see the "host 192.168.x.x is not alive"

-We started tunning the Delay control register (RGMIIDCTL) with value 0x08 i.e TX delay set to 2.25 NS

At the hardware level, we have verified that the clock and reset are fine.

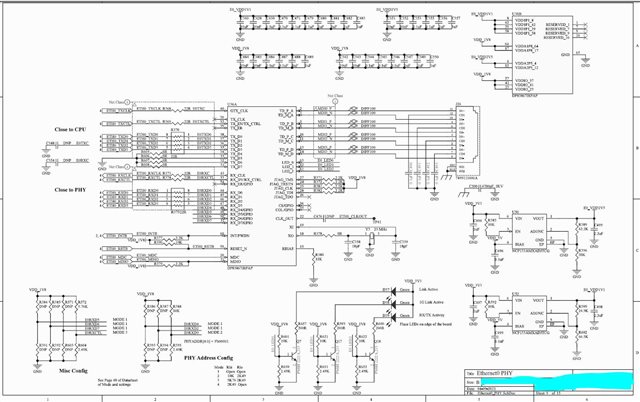

The trace lengths between the MAC and PHY interface on PCB are as follows:

We could see that if we ping from target with the delay control registers (RGMIIDCTL) set to 0x0 i.e both RGMII_RX_DELAY_CTRL/RGMII_TX_DELAY_CTRL set to 0.25 ns

the connected PC reports RX ERROR in ifconfig.

-TX_CLK: 2.5/25/125 MHz for 10/100/1000 speed gen.

-Reset: The phy is out of reset, and register/read/write looks to be working fine.

Software Aspect:

1. Bootstrap is confirmed at STRAP_STS1 and 2 registers:

We have:

PHY_ADDR: 00001

RGMII Disable is set to 0

ANEG is enabled

RGMII clock skew is enabled

2. The attached mac tx/rx packet count registers show that packets are transmitted from the target.

3. On host side, the tcpdump/wireshark tool is unable to receive any packets from the target.

4. The dt node has following entries set:

phy-mode = "rgmii-id";

phy-handle = <&phy0>;

phy-reset-gpios = <&portc 25 GPIO_ACTIVE_LOW>;

max-speed = <1000>;

status = "okay";

ti,rx-internal-delay = <7> ; -> //We have tried for the entire range from 0 to 0xf

ti,tx-internal-delay = <8> ; -> //We have tried for the entire range from 0 to 0xf

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

enet-phy-lane-no-swap;

ti,dp83867-rxctrl-strap-quirk;

5. We have also checked tuning the rx/tx internal delays over the entire valid scale of 0x0 to 0xf, but it didn't prove to be helpful.

6. The phy / mac register dump doesn't show any error event's triggered.

Could you please help us here, and let us know what we might be missing.

Please let me know if we need to share any specific information in order to analyze this better and get the issue resolved.

Thanks & BR,

Sagar Kadam