Hello Experts,

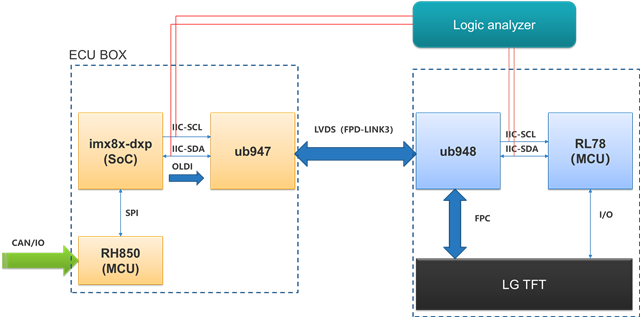

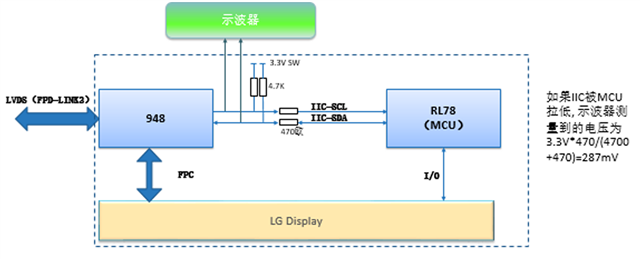

There is a black screen case: Des. is DS90UB948. Ser. is DS90UB947. DS90UB948 is connect to display via OLDI I/F.

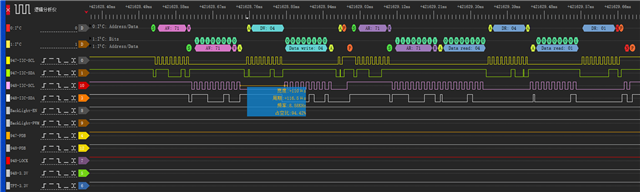

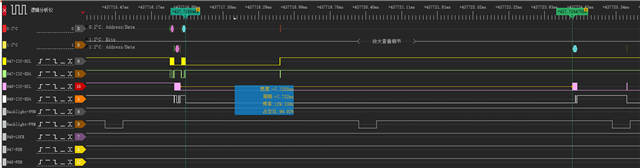

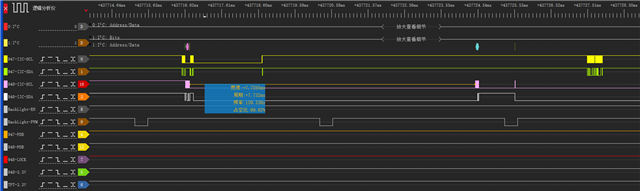

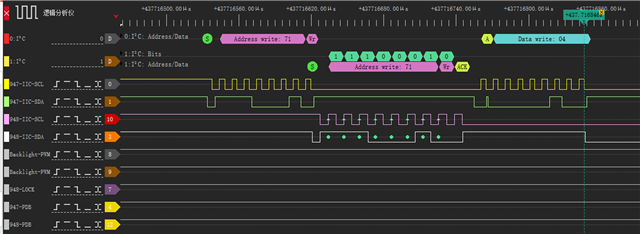

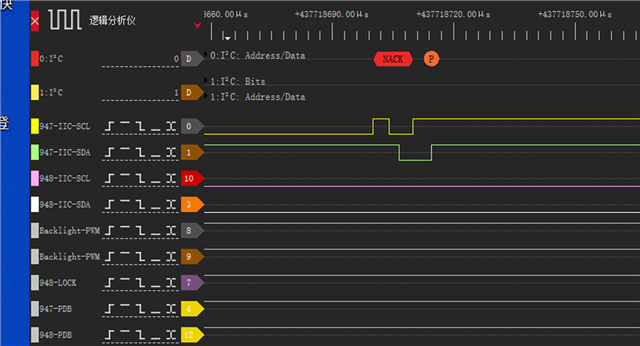

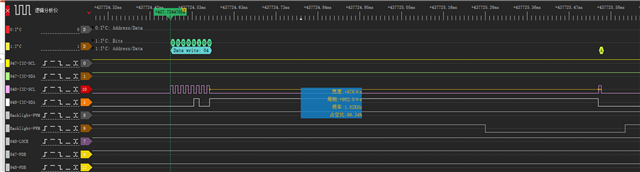

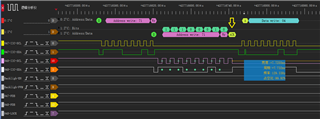

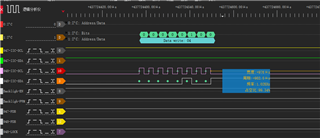

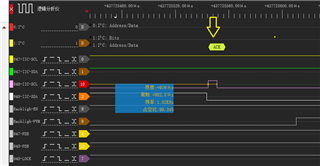

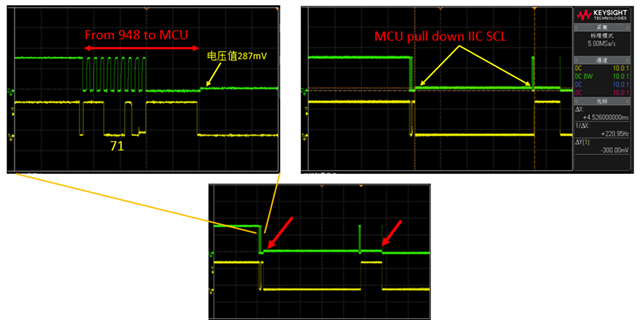

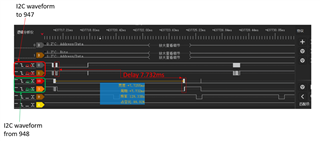

After measured, some IIC signals is delay sent out from DS90UB948 like below. When I2C signals can not be detected after such long time, display was shut down by MCU.

May I know what kindy of situation will cause such abnormal behavior? Could you share us example?

By the way, whether any failure/fault happenned on display can lead DS90UB948 sent out IIC signal delay? or other failure on DS90UB948?

If yes, could you please kindly share us more?