Hello TI engineer:

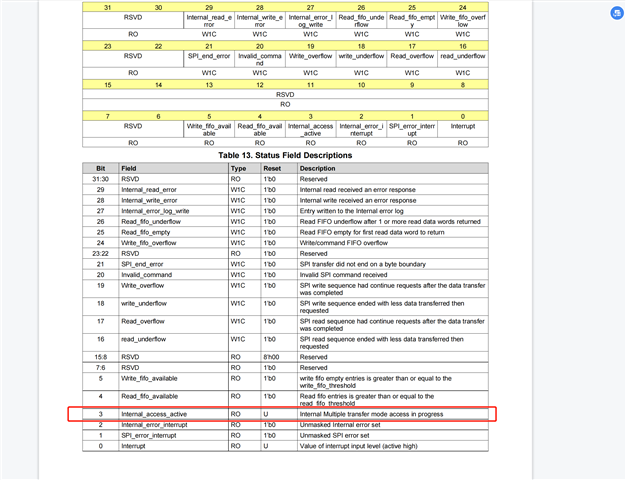

Our company is using the TCAN4550 chip, and there is a problem in use: in the normal use of the TCAN4550 chip, the bit3 of the register 0x000c (as shown in the figure below) will always be 1, but occasionally bit3 will be 0. I checked the datasheet and there is no more detailed description of this bit, may I ask under what circumstances will bit3 become 0.

Looking forward to your reply

Best regards

hanc