Other Parts Discussed in Thread: DP83TG720R-Q1

I am working with the B0.1 sample for ADC500 and not the eval board.

I had few observations regarding the additional steps required to put the DP83TG720R (1000 base T1) phy to sleep mode.

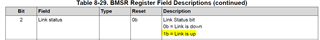

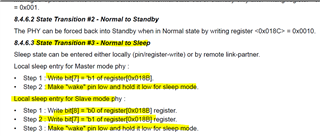

I see from the datasheet

Here we have two observation we are currently using the linux phytool commands to make to communicate with phy2

phytool write eth0/5/0xD 0x001F

phytool write eth0/5/0xE 0x018B

phytool write eth0/5/0xD 0x401F

phytool write eth0/5/0xE 0x00C0 or phytool write eth0/5/0xE 0x0080

We are using the the indirect writing of the address as mentioned in the datasheet

Observation 1:

When we dont have the media convertor connected on the respective port of 1000 base T1 and we issue the above command either from the linux console via the UART or via the ssh

We can see the inhibit pin going low which is the indication that it transit into the proper sleep.

Observation 2:

When we have the media convertor connected to the phy2 and try to issue the commands it doesnt go into sleep and i can see on the oscilloscope the phy2 inhibit pin high

Observation 3:

Suppose my media convertor is connected to the respective port of phy2 and then i issue the commands and then remove the phy2 physical connection then see on the oscilloscope i see that the inhibit pin goes low

I also kept the wakeup pin low i could see that the wakeup pin was low on the oscilloscope

What additional steps do i need to take for 1000base T1 when media convertor is connected to make it into sleep or are we missing something ?

Now with the similar steps just register number change for 100 base T1 when the media convertor is connected we trigger enable sleep bit on the 0x183 register and it goes into sleep even when the media convertor is connected so wanted to know how is the 1000 base T1 acting different from 100 base T1 and the additional steps what we need to use.