Part Number: TPS65982

Hi,

I would like to know how to set ForceLSX to 1. It's bit 23 or register 0x5F.

Please let me know I can accomplish this.

I asked this before but never got an answer: e2e.ti.com/.../tps65982-set-forcelsx

-Eric

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TPS65982

Hi,

I would like to know how to set ForceLSX to 1. It's bit 23 or register 0x5F.

Please let me know I can accomplish this.

I asked this before but never got an answer: e2e.ti.com/.../tps65982-set-forcelsx

-Eric

Eric,

This status bit is only updated when there is a TBT connection and the SBU pins need to be multiplexed to the TBT controller.

Thanks,

Chris

Hi Christodulos,

This does not appear to be true:

$ sudo i2ctransfer -f -y 0 w1@0x3f 0x6e r9 0x08 0x00 0x80 0x1f 0x47 0x01 0x00 0x00 0x00 $ sudo i2ctransfer -f -y 0 w1@0x3f 0x59 r14 0x0d 0x03 0x00 0x00 0x00 0x00 0x01 0x00 0x02 0x00 0x00 0x00 0x00 0x00 $ sudo i2ctransfer -f -y 0 w1@0x3f 0x5f r5 0x04 0x03 0x00 0x01 0x04

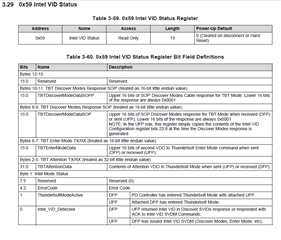

Here you can see that the LSX is pins are multiplexed to the SBU pins when in TBT mode according to the "Mux Status (Debug)" register 0x6E (bits[16:14] = 110). Additionally, you can see that it is in fact in thunderbolt alt mode since bit 1 (ThunderboltModeActive) of the "Intel VID Status" register is 1.

However, when I read register 0x5F, the ForceLSX bit is still 0.

The Technical Reference Manual also directly contradicts your statement. It clearly states that when this bit is 1 that "Force LSX connection active, regardless of TBT operation."

Since it says regardless of TBT operation, this must mean exactly that, I doubt this was written by accident.

So once again, please tell me know I can make ForceLSX become 1.

-Eric

Register 0x59 shows the first byte as 0x030D which means ErrorCode bits[4:2] = 011

This could be the result of your issue:

The least significant byte is 0x03 which is 0000 0011 in binary, meaning bits[4:2] = 000 (no error code).

But this is not at all related to my question.

Let's please get back to my actual question:

I would like to know how to set ForceLSX to 1. It's bit 23 or register 0x5F.

Please let me know I can accomplish this.

Thanks for catching that!

I do not know your configuration but the Status is set when needed so in your design it must not be needed. Is this causing issues in your design?

We want to be able to multiplex the LSX pins to the SBU pins manually, without having to enter thunderbolt alt mode. We are able to multiplex the pins by entering thunderbolt alt mode but that is not our goal.

Please let me know how I can make ForceLSX become 1, which clearly states "Force LSX connection active, regardless of TBT operation."

Eric,

I think the confusion is that there are different TBT operating modes (legacy and non-legacy) and when it says regardless of TBT operation it is still referring to be in the alternate TBT mode but does not care about the operating characteristics of the mode.

If your goal is to mux these pins then consider using a GPIO Events here to control a SBU MUX:

Christodulos,

When you say "to control a SBU MUX" do you mean a multiplexer that is external to the TPS65982 or are you referring to the interal SBU crossbar multiplexer of the TPS65982?

The goal is to use the TPS65982's SBU crossbar multiplexer to MUX the LSX pins to its SBU pins without having to enter TBT alt mode, which is what led us to the ForceLSX bit and its description which gives the impression that it would achieve exactly this goal.

We are not using an Intel reference design. We are entering TBT mode solely for the LSX to SBU muxing, so we can use it for debug purposes.

Our product officially supports displayport alt mode, but thunderbolt alt mode is only being used for debugging. Hence why we want to be able to multiplex the LSX pins to the SBU pins without having to rely on the TPS65982 entering thunderbolt alt mode.

It is a status (Read-only) bit and the name is a bit mis informative but yes there is no way to force the MUX without being in TBT mode.