Hi Team,

There is a good new that we DIN DS90UB935TRHBRQ1!!!

And still need your support to make sure DWIN DS90UB935TRHBRQ1 , THX

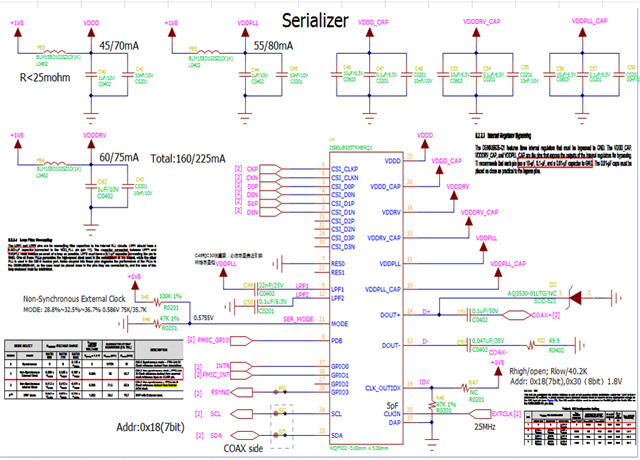

Please refer to attachment for the clearer SCH,

1. Does the module peripheral circuit design meet the DS90UB935TRHBRQ1 requirements?

2. The POC recommendation of 935 is shown in the schematic sheet. It may be possible to use two levels to meet the requirements. Please provide the corresponding test data. Does this project meet the requirements with three levels?

3. Do the power supplies VDDD, VDDPLL and VDDDDRV have to be connected with magnetic beads?

4. What is the voltage of pin12 (LPF2)? Is it sufficient to use a 6.3V withstand voltage capacitor?

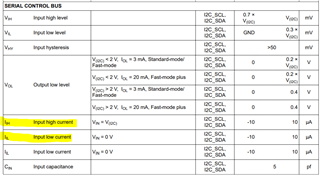

5. SCL and SDA are open-drain state, what is the actual internal resistance? How much current sink capability does it have? Does the pull-up 1.5K meet the requirements?

6. The ESD test on the coaxial pin was not prevented from causing damage. A reserved ESD device was added on pin14 (Dout+). The parameters of the ESD device are as follows. Does it affect the signal? Or what parameters need to be met to use?