Part Number: SN65DSI84

The screen uses the following timings (dual link lvds):

clock = 74250, /* kHz */

horizontal active = 1920

horizontal front = 20

horizontal sync = 240

horizontal back = 20

vertical active = 1080

vertical front = 2

vertical sync = 41

vertical back = 2

Using format 1, 24 bpp, DE+, HS-, VS-

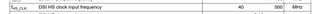

I configured the mipi interface to use the same timings, 4 lanes, RGB888 - dsi clock A @ 445.5MHz

I use the dsi tool (see output below) & calculated everything by hand (resulting in the same register settings)

My issues:

- Regular mode: I don't have an image. Only a black output on lvds. (though I can measure there is data on the mipi lines) Error register E5 shows 0x01 -> pll didn't lock. I don't know why the pll didn't lock. Mipi clock seems stable when I measure it.

- Test image: There are bars visible on screen. I can measure the lvds clock, and it is correct. (74.xx Mhz) However, the screen flickers.

I included my settings in a tar file, since I can't upload a *.dsi file.

I'm not sure what is going wrong, or what I can try next. Can you spot any misconfiguration? Or give some clue to continue?

Thanks