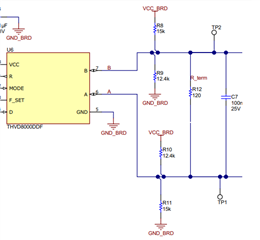

Other Parts Discussed in Thread: THVD8010

Hi team,

I have been doing some measurements for pre-compliance of railway norm (0Vrms conducted noise with 80% AM at 1kHz, from 150kHz to 80MHz) and ... I don't manage to pass : the Amplitude Modulation at 1kHz looks like a 1kHz OOK modulation for the THVD8000.

There are some problems with my setup and I know it but not everything can be as perfect as we hope (even in the final implementation in the train) :

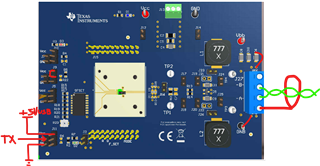

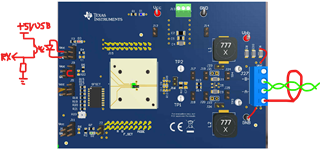

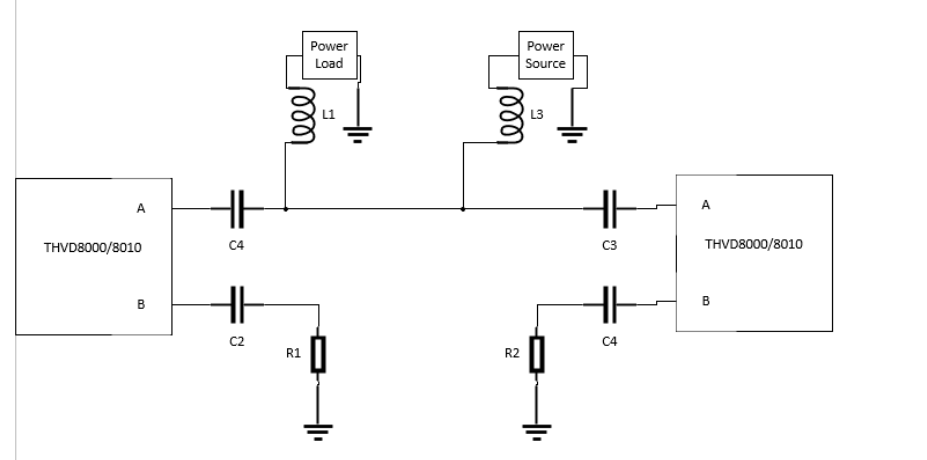

I'm using 2* THVD8000 evaluation modules, one with a USB-uart adapter with the THVD configured as always TX, the 5V USB power powering the local board and the 10m away board through the PLC components, then a 10m cable loop, another EVM configured as always RX and returning data over optocoupler to the initial USB-UART adapter (both EVM as taped back to back (20mm away from each other).

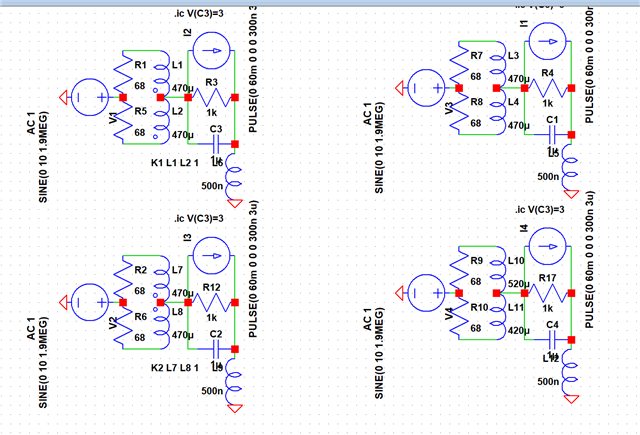

The 10Vrms conducted is done on the shielded cable (didn't have a 120Ohm railway compliant cable as it will be in the train laying around so I'm using a normal shielded 0.75mm² cable)

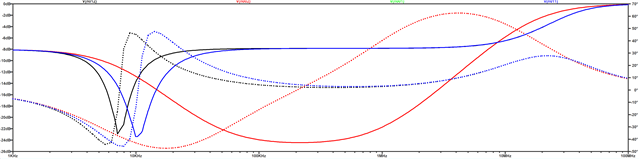

The EVM are set for 5MHz modulation and common mode noise translates to differential somehow (pickup coils that are +/-20% variation?) at around 5 & 10MHz (+/-20% around those fundamental and first harmonic)

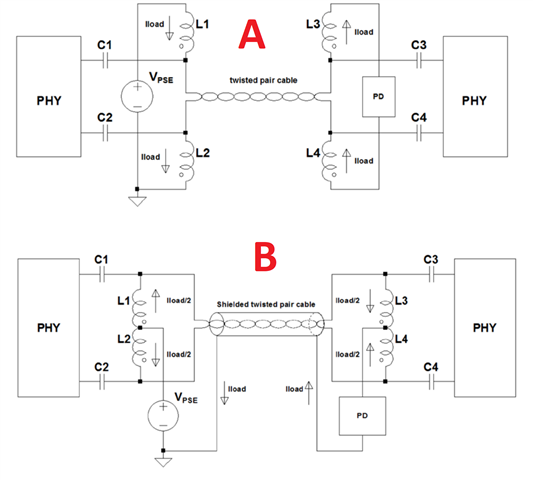

I tested replacing the L-C extraction/injection by a PoE transformer (wurth split primary) but I got info from them that if used with DC current (with differential current, not common mode) the transformer saturates, and from my measurements it's even worse for common mode noise immunity than L-C.

I've yet to test a power choke dual coil (to have better matching between inductors = less common to differential noise translation) and to use the cable shield as negative conductor (see page 3 of https://www.ieee802.org/3/cg/public/Sept2017/stewart_01_0917.pdf)

Thanks for your suggestions, help, ect.