Other Parts Discussed in Thread: ALP

Hi team,

- For UB936 power up sequence, why need to hard reset like below figure?

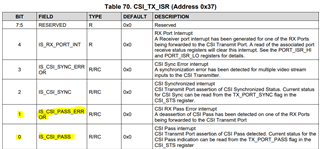

- What is the meaning of 0x37 bit 0 and 1? If they are both set, what is the meaning?

BR

Jiawei

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

BR

Jiawei

Hello Jiawei,

Best,

Justin Phan

Hi Phan,

Thanks for your reply. Could you kindly tell me how to fix AEQ? Just configure 0xD4? Is there a configuration order? And how to check we have configure right?Thanks!

BR

Jiawei

Hello Jiawei,

On the 936, the AEQ will loop through a default range of EQ and Strobe settings in order to recover the data being sent from the SER->DES. Typically, customers do not need to configure the AEQ, since the AEQ will recover the serial data through a range of aging and temperature conditions.

Are you unable to achieve a stable LOCK between your 936 and serializer device?

You could run the MAP tool on ALP to check the quality of your channel link between the SER->DES and adjust the AEQ settings in the 936, by referencing the following App Note:

But this is typically a temporary fix and customers may find difficulties in achieving passing performance across multiple devices in production. We actually recommend reviewing the Insertion Loss, Return Loss, and Impedance of the channel link and making improvements in the system design to achieve stable LOCK, without needing to modify the default AEQ settings.

Best,

Justin Phan

Hi Phan,

Thanks for your comments here, We do meet unlock issue in 933>>936. For unlock issue, could we have another debug direction expect margin analysis? But I also want to understand how to fix AEQ, could you kindly also give the answer here? Thanks!

BR

Jiawei

Hi Jiawei,

1) Just to clarify on the unlock issue, do you mean that when you read register 0x4D on the 936 multiple times, do you see the LOCK_STS_CHG bit constantly changing?

In a stable LOCK situation, we expect to see the LOCK_STS bit set to 1 and the LOCK_STS_CHG bit remain constant at 0 after multiple register reads to register 0x4D.

2) Could you also run the MAP tool in ALP on the 936 and post the results?

There is typically no issue with the AEQ on the 936 device itself. If the 933->936 are frequently LOCKing and unLOCKing, then this is likely a system-level issue and we recommend making improvements in the design. Could you first answer the above 2 questions, so that we can determine a debug direction?

Best,

Justin Phan

Hi Phan,

As customer are really push on this, I think we need more directions, thanks!

BR

Jiawei

Hello Jiawei,

Best,

Justin Phan

Hi Phan,

Thanks for your reply. Could you kindly also check 936 code? Any questions pls let me know!

BR

Jiawei

Hello Jiawei,

A few comments:

Best,

Justin Phan

Hi Phan,

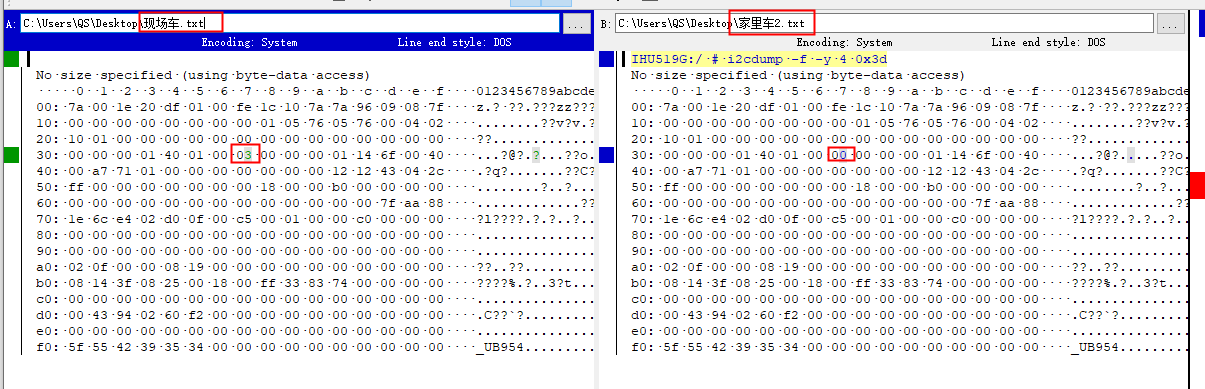

Thanks for your reply. I met another black issue (won't recover until power off and power on) and at this moment lock is high and 0x73-76 are stable. Below is the registers dump of abnormal (left) and noraml (right).

For the black issue, could you also kindly share your comments and debug directions here? Appreciate!

BR

Jiawei

Hello Jiawei,

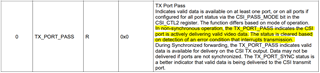

The only difference between the abnormal and normal scenarios is that register 0x37=0x03 in the abnormal situation, but register 0x37=0x00 in the normal situation. There are no errors detected at the RX Port on the 936 and LOCK does seem stable.

Best,

Justin Phan