Other Parts Discussed in Thread: TMDS181

Hi,

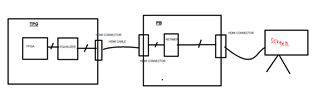

We have board lets call it TPG(Test Pattern Generator board) that include FPGA that transmit constant pattern(it doesn't need HPD/I2C/CEC etc.) and routed to equalizer and from equalizer(from another company) to HDMI connector - this is the source side.

Here is the part of the schematic from the TPG side:

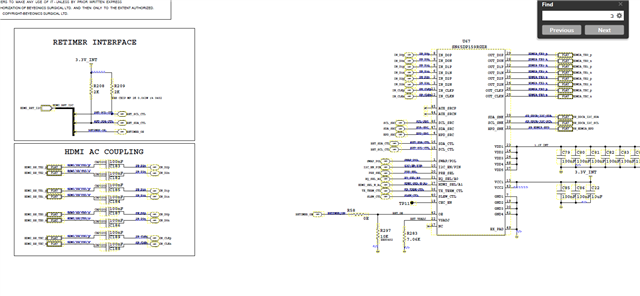

In my board that Im using lets call it PB this is the sink side, the signals comes from HDMI connector (the TPG is connected to my board trough HDMI cable) and routing to TI RETIMER :SN65DP159RGZR

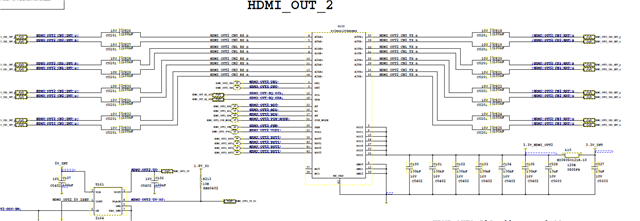

Here is part of the schematic(with not include the HDMI connector ):

simplified block diagram :

The problem:

in the PB - at the output of the Retimer there is a connection to the screen with another HDMI connector,

and the screen does not RECIEVE the video that the TPG transmits,

but if for example I take the cable that is connected to the TPG and connects to the screen directly(see some video) then back to my PB card,

suddenly the signals are received properly and I see them on the screen.

I would expect that if there was a problem of detection then it will continue to be,

it is important for me to note that there is no HPD and it is not even connected at all on the side of the TPG.

It seems that the equalizer does not recognize the retimer.

This is an HDMI 2.0 broadcast

what could be the problem?

if you need any information Ill attach it ,

thanks.