Hi Team,

I have a question about TIOS101 abso max ratings and driving inductive loads.

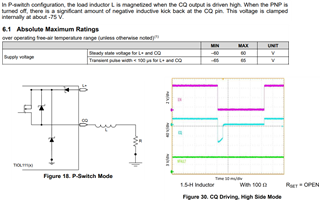

TIOS101 CQ pin abso max is ±65V(transient pulse width < 100us for VCC and OUT).

"9.2.2.3 Driving Inductive Loads" mentions a significant amount of inductive kick back is clamped internally at about ±75V.

How do we consider the relationship between ±65V and ±75V?

If we use inductive load and its significant amount of inductive kick back exceeds ±65V, TIOS101 has internal clamp diode so it is no problem even though it violates ±65V abso max?

±75V is not described in abso max spec so I'm not sure ±75V is just for protection.

±75V is just protection so we have to follow abso max spec or we can say that device can support up to ±75V under driving inductive loads?

Regards,

Kai