Hi team

Our customer is using DP83826E for their own real-time network, it's configured with ENHANCED MODE. The timing is

1. power up

2.After 300ms,FPGA reset DP83826, and keep write CR2 Bit 1 as 1, to disable Odd-Nibble Detection.

It works for most of time, but sometimes when power up again, the link can't establish.

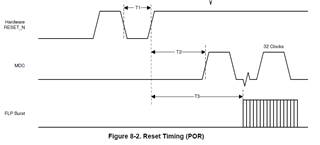

We're wondering that is it due to the writing while SMI is not ready? Because it need T2-2ms for SMI.