Part Number: TCAN4550

I asked a few days about available registers without the crystal. Finally I received them, and assembled them.

Part number: ABM11W40.0000MHZ8B1UT and 8pF caps.

However, I'm confused about the crystal spec in the datasheet. High level input between 0.85-1.1 VIO and Low <0.3 VIO.

VIO at 3.3 would be L=<0.99V and H=>2.805V.

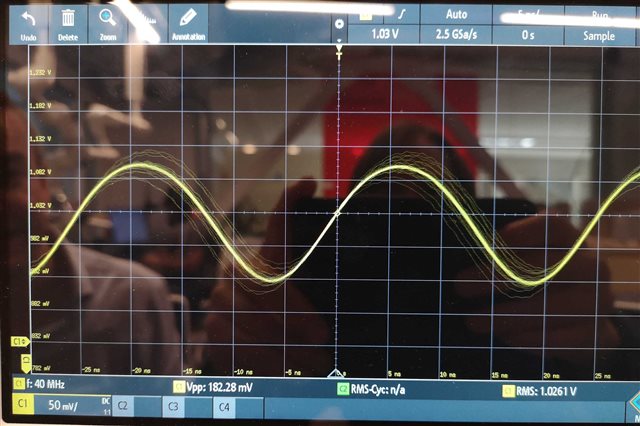

But on the scope (probing OSC1), i get 182mVp-p which swings around 1V.

Is this correct?