Dear Ti,

I use the ds90ub960 deserializer to receive the data transmitted by the camera.

The internal serializer of the camera is ds90ub935.

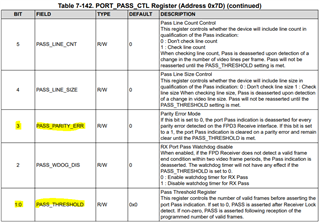

However, when I read the 0x4d register, its value is 0x39, indicating that the received input does not meet the pass criteria.

Can you help me see why?

The deserializer and serializer can communicate through I2C, and the camera can send data as soon as it is powered on.

The data format is raw16, and the lower 12 bits are valid.

Xinyu.