Part Number: SN65LVDT41

Other Parts Discussed in Thread: SN65MLVD040, SN65LVDM31

Hello

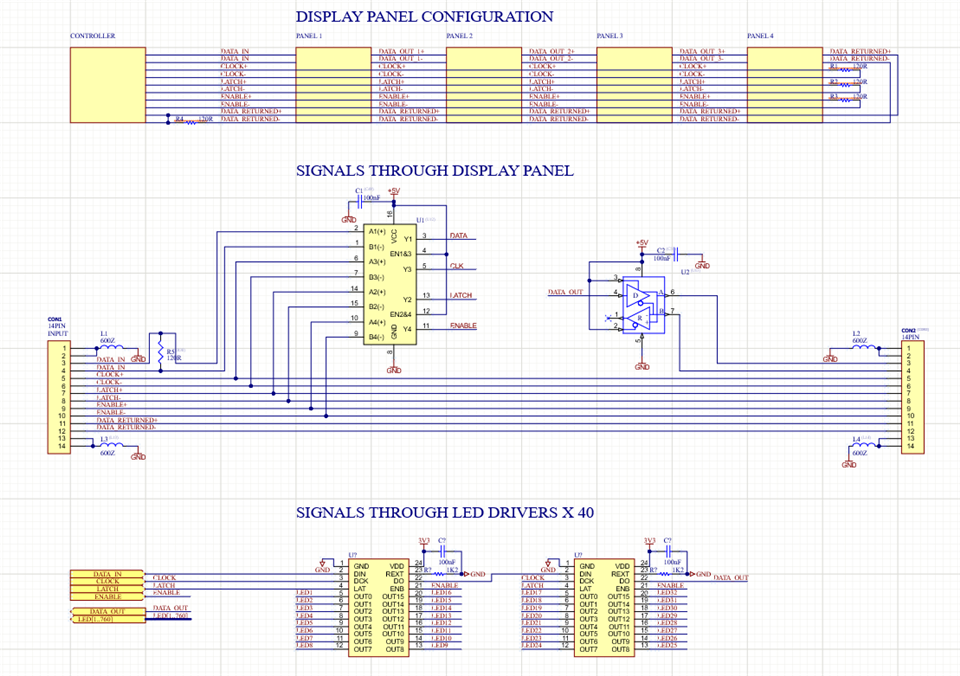

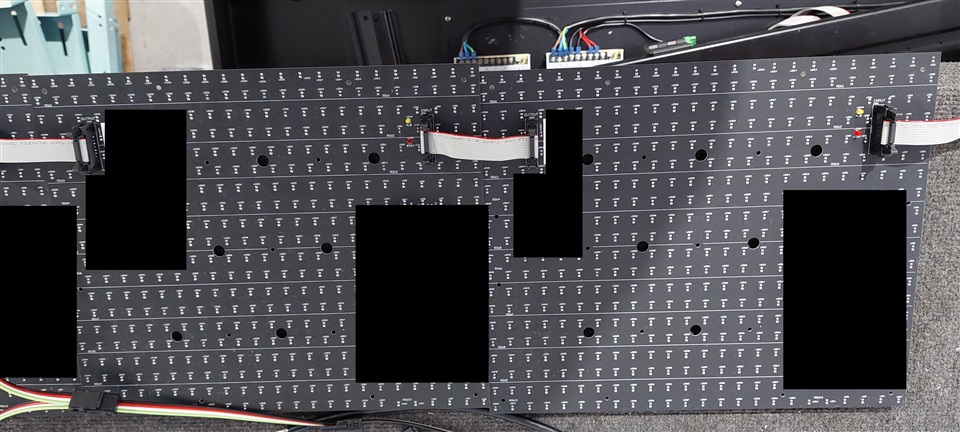

I am trying to send 215,040 bits of data across 21 LED display panels which add up to a length of 7.3m.

We are currently using RS485 drivers to send the data across all the LED panels.

The clock, latch and enable signals are configured as multidrop whilst the data is sent as point to point as it must go through 40 LED drivers on each panel.

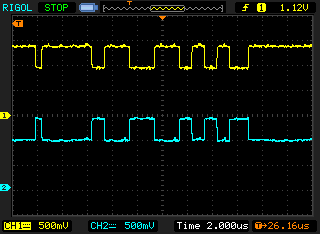

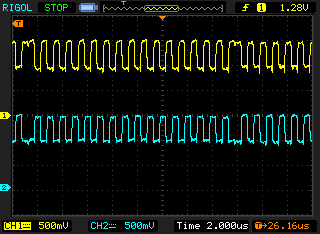

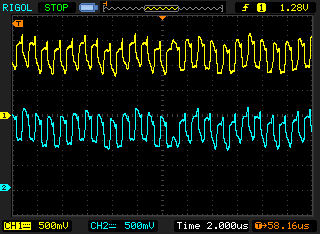

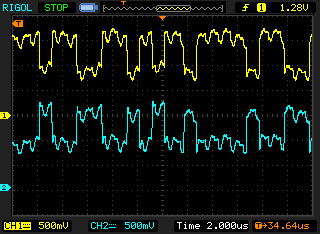

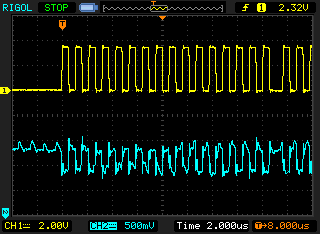

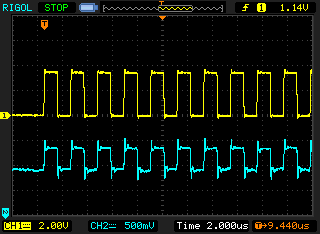

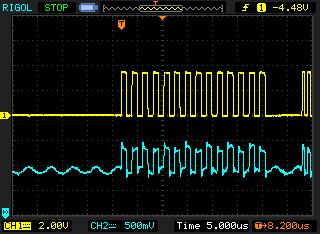

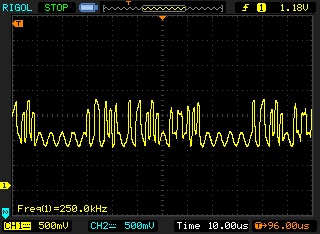

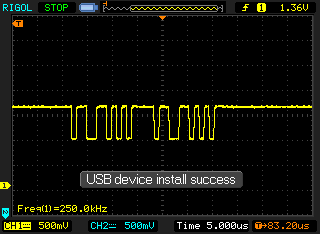

The problem is we can't get the speed needed to update the signs quick enough using RS485 so we are testing out LVDS technology.

I have just tested the SN65LVDT41 as a quad driver and SN65LVDS32PW as a quad receiver, then the data output will get sent out by SN65LVDM176DR driver.

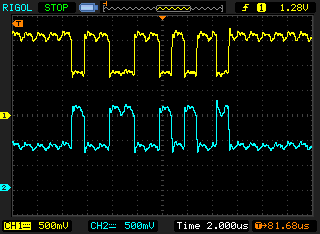

Unfortunately I was only able to drive 5 panels successfully which is roughly 1.75m and I was expecting to be able to drive about 10m.

Can anyone explain to me where I might be going wrong?

Would it be possible to go point to point between each panel so all the signals are going in and out of each panel that are connected over 21 panels then the data returned back through all the panels and back to the controller?

I have also seen that M-LVDS may be able to drive longer distances which is what I am going to test next as converting the PCB to point to point will call for a PCB change.

The signal traces also go through about 40cm of PCB so wondering if that is also causing issues and if the connectors on the PCB should be moved closer together to minimize the length of the PCB traces and increase the cable length.

We are also only using ribbon cable into a 14 pin IDC header so wondering if that could also be causing some issues.

Any information and guidance will be greatly appreciated.

Thanks

Craig