Hi expert,

I have two questions regarding to the VDDIO/Vsleep and WAKE pin.

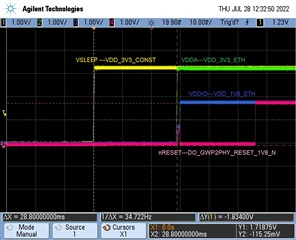

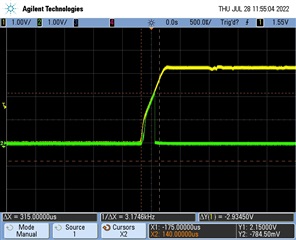

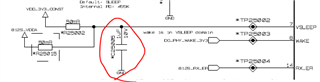

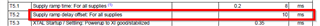

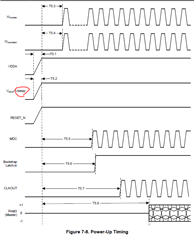

- For the power up sequence, what the maximum acceptable delay time spec for Vsleep and VDDIO? In customer's real application, the Vsleep must power on first, then they can enable VDDIO power rail. So they need to consider the delay time spec between VDDIO and Vsleep. Is it limited in 10ms? Customer measure the current delay time between VDDIO and Vsleep which is higher than 10ms. But the 812 can power up into normal mode normally. So just would like to check with you.

2. During power up and normal operation, how to deal with WAKE pin? For local wake up from sleep mode, we can pull a >40us high level pulse on WAKE pin. So does it mean that WAKE pin can be kept low in other states?

Thanks!

Ethan Wen