Hi,

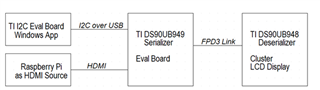

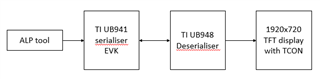

1. UB949 is able to get timing parameters right for the display (which require TCON to be configured) for the data coming from HDMI source.

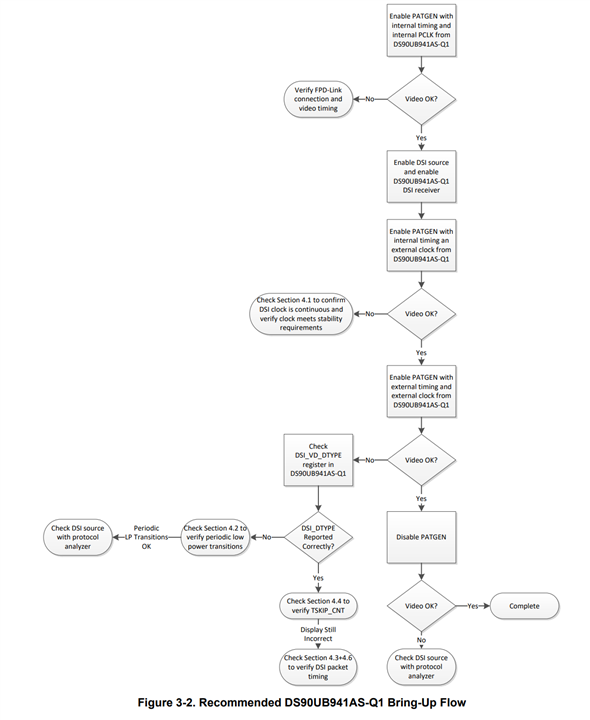

2. Whereas with UB941 we are only able to generate test patterns successfully for that display but not the data coming from MIPI

We believe UB949 serializer is similar to UB941 apart from supporting HDMI instead of MIPI. In that case can we get configurations to get MIPI data to be

coming on the display without any TCON configurations (for now we arent having the support to configure TCON in our design hence wanted to utilize the test pattern generation method to get our mipi data in the display)

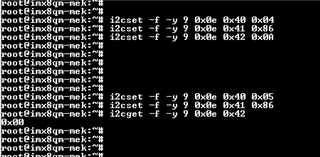

Below is the list of i2c registers we are writing to generate test pattern from UB941 serializer to the display

i2cset -y -f 9 0x0e 0x01 0x08 # REG:RESET_CTL --> Disable DSI

i2cset -y -f 9 0x0e 0x1E 0x01 # REG:TX_PORT_SEL --> Select FPD-Link III Port 0

# Auto-Scrolling Configuration

i2cset -y -f 9 0x0e 0x66 0x0F # Enable PGFT Register

i2cset -y -f 9 0x0e 0x67 0x1E # This sets the frame timer to 60

i2cset -y -f 9 0x0e 0x66 0x10 # Enable PGTSC Register

i2cset -y -f 9 0x0e 0x67 0x03 # This sets the number of active patterns to 3

i2cset -y -f 9 0x0e 0x66 0x11 # Enable PGTSO1 Register

i2cset -y -f 9 0x0e 0x67 0x43 # This sets Pattern 1 to Red (3) and Pattern 2 to Green (4)

i2cset -y -f 9 0x0e 0x66 0x12 # Enable PGTSO2 Register

i2cset -y -f 9 0x0e 0x67 0x05 # This sets Pattern 3 to Blue (5); Pattern 4 is ignored

# Set Pixel Clock(66.66 Mhz)

i2cset -y -f 9 0x0e 0x66 0x03 # enable PGCDC1 Register

i2cset -y -f 9 0x0e 0x67 0x03 # to set the clock divider to be 3 (200/87.96)

# set Active Frame Size (Horizontal width= 1920 pixels and Vertical width= 720 pixels)

i2cset -y -f 9 0x0e 0x66 0x07 # enable PGAFS1 Register

i2cset -y -f 9 0x0e 0x67 0x80 # to set desired Active Horizontal Width

i2cset -y -f 9 0x0e 0x66 0x08 # enable PGAFS2 Register

i2cset -y -f 9 0x0e 0x67 0x07 # to set desired Active Vertical and Horizontal Widths

i2cset -y -f 9 0x0e 0x66 0x09 # enable PGAFS3 Register

i2cset -y -f 9 0x0e 0x67 0x2D # to set desired Active Vertical Width

# Set Total Frame Size(Horizontal width= 2000 pixels and Vertical width= 758 pixels)

i2cset -y -f 9 0x0e 0x66 0x04 # enable PGTFS1 Register

i2cset -y -f 9 0x0e 0x67 0xD0 # to set desired Total Horizontal Width

i2cset -y -f 9 0x0e 0x66 0x05 # enable PGTFS2 Register

i2cset -y -f 9 0x0e 0x67 0xD7 # to set desired Total Vertical and Horizontal Widths

i2cset -y -f 9 0x0e 0x66 0x06 # enable PGTFS3 Register

i2cset -y -f 9 0x0e 0x67 0x2D # to set desired Total Vertical Width

# Set Back Porch. H Back Porch: 32 pixels, V Back Porch: 5 pixels

i2cset -y -f 9 0x0e 0x66 0x0C # enable PGHBP Register

i2cset -y -f 9 0x0e 0x67 0x20 # to set desired Horizontal Back Porch Width

i2cset -y -f 9 0x0e 0x66 0x0D # enable PGVBP Register

i2cset -y -f 9 0x0e 0x67 0x05 # to set desired Vertical Back Porch Width

# Set Sync Widths. H Sync Width: 16 pixels, V Sync Width: 2

i2cset -y -f 9 0x0e 0x66 0x0A # enable PGHSW Register

i2cset -y -f 9 0x0e 0x67 0x10 # to set desired Horizontal sync Width

i2cset -y -f 9 0x0e 0x66 0x0B # enable PGVSW Register

i2cset -y -f 9 0x0e 0x67 0x02 # to set desired Vertical sync Width

# Set Sync Polarities

i2cset -y -f 9 0x0e 0x66 0x0E # enable PBSC Register

i2cset -y -f 9 0x0e 0x67 0x03 # to set desired horizontal and vertical sync widths to "Negative"

# Internal Default Timing Configuration

i2cset -y -f 9 0x0e 0x65 0x05 # enable Auto-Scrolling with internal timing

i2cset -y -f 9 0x0e 0x64 0x11 # enable the pattern generator

i2cset -y -f 9 0x0e 0x01 0x00 # REG:RESET_CTL --> Enable DSI

Thanks & Regards

Musthafa av