hi,

+-------------+ 4 lanes +-------------+ +-------------+ +-------------+ | MIPI0|------------>|DSI0 OUT0|------------>|IN0 LVDS0|------------>| TFT LCD | | SPI |<----------->|SPI | FPD-Link3 | | single OLDI | 1920*720 | | SOC | | UB941 | 2 lanes | UB948 | | | | | | | STP | | | | | IMX8QM | |DSI1 OUT1|------------>|IN1 SPI |------------>| SPI |

+-------------+ +-------------+ +-------------+ +-------------+

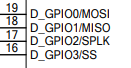

How to enable SPI pins and SPI communication between serialiser and deserialiser

we are using ub941 seriliaser and ub948 deserialiser

which are the registers needs to be configured on ub941 and as well as ub948?

we need to implement spi commuincation from Application processor to TFT display as shown in the above image.

kindly revert back asap on this

Thanks,

Musthafa av