Hi,our team used DS90UB947-Q1 together with Sunplus 8368P.

The output frequency of 8368P 's LVDS clock will fluctuate +/- 3MHz occasionally, so I want to know how we can set the 947 to prevent the PPL form being reset?

Best Regards.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,our team used DS90UB947-Q1 together with Sunplus 8368P.

The output frequency of 8368P 's LVDS clock will fluctuate +/- 3MHz occasionally, so I want to know how we can set the 947 to prevent the PPL form being reset?

Best Regards.

Hi Yao,

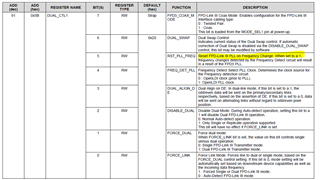

Register 0x5B bit 5 is set to 1 by default. This will reset FPD-Link III PLL on frequency Change detected and will result in a reset of the FPD3 PLL.

So setting it 0x5B[5] to zero will prevent the PLL from resetting. Please be careful with the PCLK frequency though. If it changes too much, it will cause problems. For now let me know if this fixes your issue.

Regards,

Fadi A.

Hi Fadi,

Thank you very much for your reply, the screen display was still shaking after we set the register 0x5B[5] of 947 to 0, so we checked 948 together with 947 and measured the signal of 948, we found the 948 would losing lock when the LVDS clock is fluctuating.

So we want to know how we can set the 948 to prevent it losing lock in this case?

Best Regards.

Hi Yao,

Unfortunately, with such gross LVDS clock +/- 3 MHz fluctuation, the 947 output data will get corrupted which will causing the 948 lock signal to lose lock due to data corruption caused by the LVDS CLK fluctuation on the 947 side.

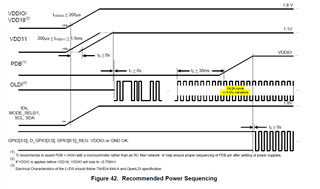

The main issue is not in the 948 lock side or the 947 PLL side. The issue is that your CLK fluctuation is out of spec for what the 947 recommends in the datasheet - see datasheet image below.

Refer to 9.1 Power-Up Requirements and PDB Pin in the 947 datasheet for more details.

OLDI clock variation should be +/-0.5% per device spec.

Regards,

Fadi A.