Other Parts Discussed in Thread: TUSB8042

Hello.

In our circuit, after the TUSB8042A is powered up, the config setting is executed from the HOST via the SMBUS interface.

The hard configuration setting pin of TUSB8042A is set as follows, and it is set in SMBUS.

◇HARD STRAP PIN setting

・SMBUSZ/SS_SUSPEND:Pulldown with 2.2KΩ(LOW:SMBUS Mode SELLECT)

・SCL/SMBCLK:Pullup with 1KΩ

・SDA/SMBDAT:Pullup with 1KΩ

・FULLPWRMGMTz/FULLAUTOz/SMBA1/SS_UP:Pulldown with 4.7KΩ(LOW:SMBUS ADDRESS1)

・GANGED/SMBA2/HS_UP:Pulldown with 4.7KΩ(LOW:SMBUS ADDRESS2)

・PWRCTL_POL:Pullup with 4.7KΩ(HIGH:ACTIVE HIGH)

・AUTOENz/HS_SUSPEND:Pullup with 4.7KΩ

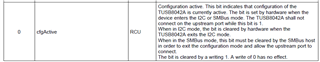

After the power-up, I cleared the cfgactive bit (bit0) of Register 0xF8h by writing 1 from the SMBUS interface of HOST.

However, the cfgactive bit did not change from 1 to 0 and could not be cleared.

However, for registers other than address 0xF8, writing and reading were possible normally, and there was no problem.

Please tell me the following points.

【Q1】

Is there any reason why the cfgactive bit (bit0) does not change from 1 to 0?

Please let me know if there is any cause.

【Q2】

I want to check if there is a procedure to clear the cfgactive bit.

Is there a TUSB8042A configuration manual when using the SMBUS interface from HOST?