A. We are currently working on the following hardware configuration:

-ECU connect to de-serializer 934

-Image sensor (0x10) connected to 933(0x58) on the other side

B. Problem

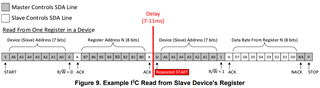

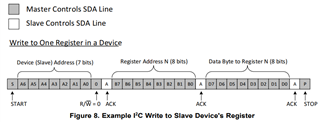

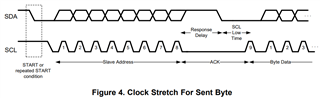

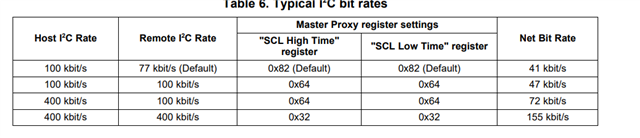

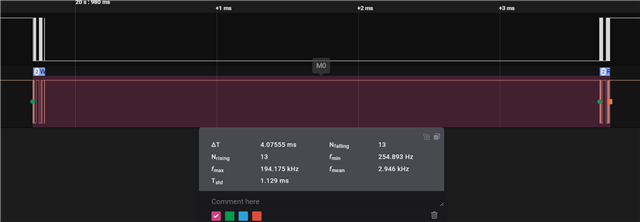

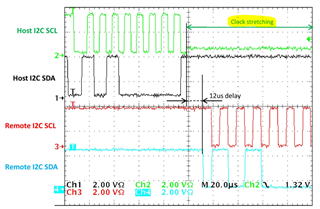

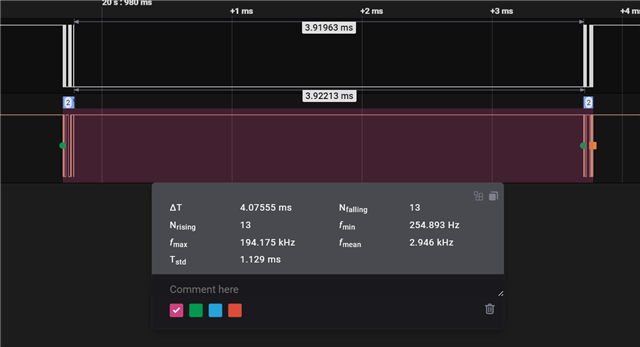

We observe that a single byte read from serializer is redding an undefined value if the 2 parts I2C read transaction ( WR to set register address and RD to get back register value) are separated by register write commands( to the sensor).

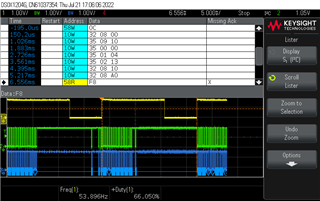

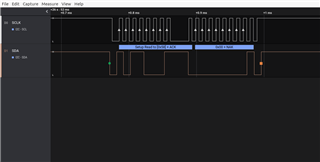

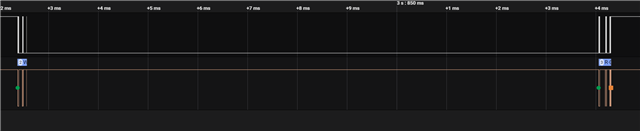

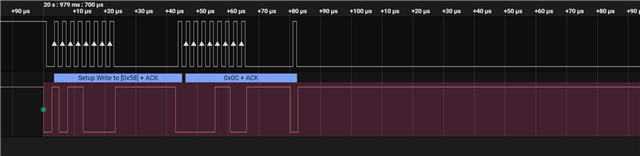

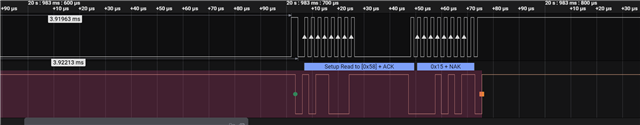

Please refer the logic analyser capture shown below. Read transaction with serializer (58W + 58R) is split by the high priority sensor (10W) transactions. Expected value is 0x11 (returned during uninterrupted/atomic read) but 0xF8 is read which seems to be a random value unrelated to the register address previously requested.

So questions are:

-Is interleaved register read command to the serializer a legal transaction?

-What could be the reason for the problem

-Is there any configuration to the back channel we should look at?

(The first WR)

(The first WR)