Part Number: SN65HVD09

Hello,

we had the emc test with our new product last week. On this product also sits a SN65HVD09.

All 9 channels are occupied and the function is basically given. We control a RGB LED matrix display and need besides the RGB channels also 2 clock signals, a latch signal and control signals.

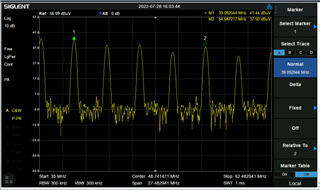

The clock signals have a frequency of 4MHz (see oscilloscope picture).From my point of view, the signals on the RS485 side look quite good and even with a longer line the edges are still steep enough to be detected safely.

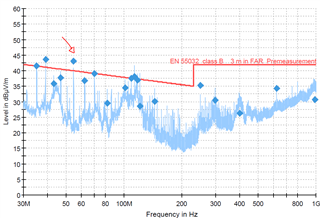

On the original image from the test lab, the limit has been exceeded in some places in the range from 30MHz to 100MHz.

As it turned out, these peaks come from the SN65HVD09

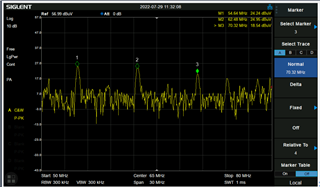

Back in the office, we used a near-field probe and a spectrum analyzer to remeasure the situation. Even with an EMI Antenna from 3m away, the interference levels can be seen. However, we can't find the reason why the SN65HVD09 is radiating so much at this point. When we switch it off, all interference levels are gone.

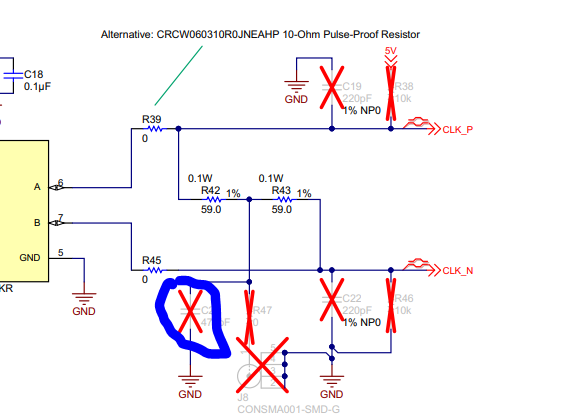

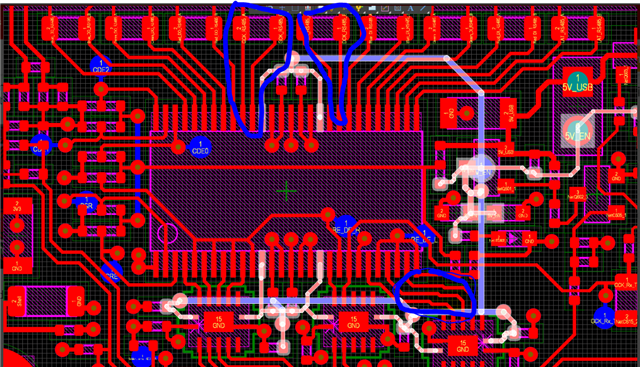

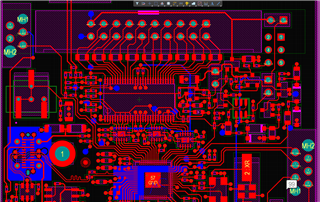

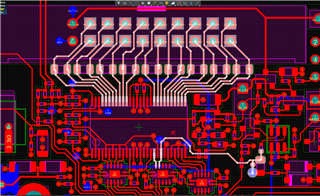

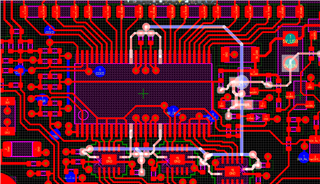

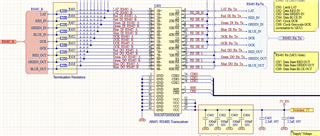

Here is the layout and the schematic:

the marked lines (top layer) are the 5V supply lines. Layer 2 has GND throughout and layer 3 has 3.3V throughout.

We are grateful for any input and do not know where we could optimize.

Thanks already for the help

Boris