Other Parts Discussed in Thread: TXS0104E, TCA9800, LSF0102

Hi,

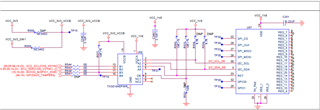

We are using this part for I2C Level Translation.

Our Host Processor Works on 3.3V and Slave IC is on 1.8V. That is why we used Level Translator here in between. Please refer to the below schematic.

But we found here Communication is failed.

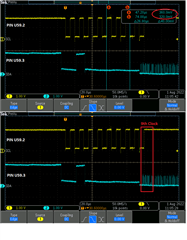

When I use TXS0104E, it's I2C Waveform in our board is as below and below is our observations.

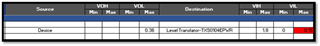

- Low Voltage (VL) of both SCL and SDA is not absolute zero here, there is 0.36V.

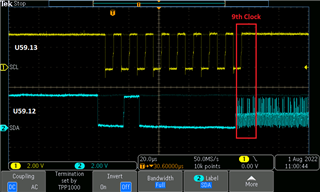

- During the 9th clock pulse, the slave is trying to pull the bus low, and due to the 9th clock extension SDA also retaining in LOW.

And below is the I2C waveform of U59.13 and U59.12 pin.

Kindly suggest solving this issue.

Regards,

Chitharanjan