Other Parts Discussed in Thread: DS90UB928Q-Q1, DS90CR287

Hi Team,

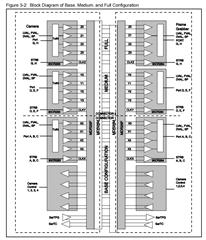

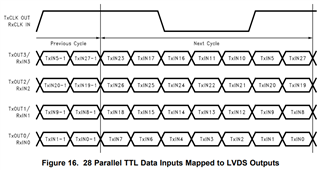

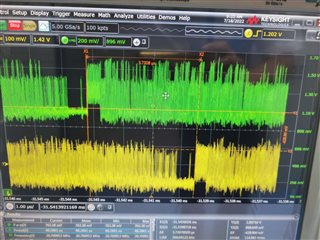

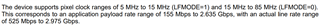

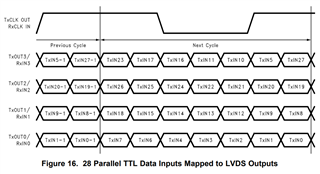

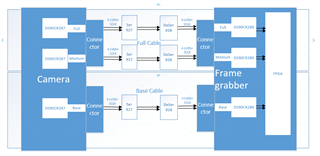

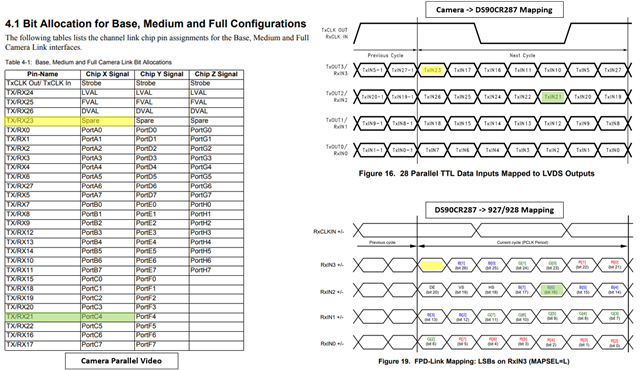

I used DS90UB927Q-Q1 and DS90UB928Q-Q1 for camera link cable;As you know, camera link has those work mode like base/medium/full/80 bit mode. when the ICs work in 80 bit 10tap8bit mode, image display abnormal.

The abnormal display is as follow.

I would like to ask you two questions as follow:

1.Do DS90UB927Q-Q1 and DS90UB928Q-Q1 support camera link working in 80bit 10tap8bit mode?

2.If the ICs cannot support the 10tap8bit mode, Do you have any other chipsets to recommend for camera link 10tap8bit mode?

Thanks!

best regards

DonCheng