Dear expert,

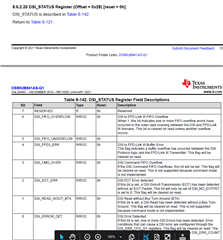

Customer rely on DPHY_STATUS, DPHY_DLANEx_ERR register to indicate any DSI related err during mass production.

They did some test to verify our DSI related err and find it doesn't match.

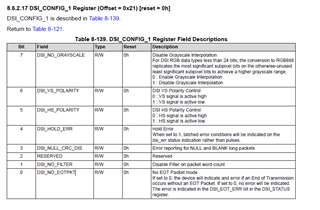

They increase/decrease HS_Trail duration on purpose from SoC to create EOT problem on purpose.

You can refer to below attachment. The boards under test are good boards.

At colomn D, L, when HS_Trail is 86ns, 86ns, which is within spec , but DPHY_STATUS, DPHY_DLANEx_ERR report error.

And At colomn L, when HS_Trail is 339ns,which is out of spec , but DPHY_STATUS, DPHY_DLANEx_ERR doesn't report error.

DSI clock is 320MHz, UI=1.5ns

HS_Trail need to >60ns+4UI=66ns

Teor need to <105+12UI=123ns

Treot is measured as 12ns

Then HS_Trail should <Teor-Treot =111ns

Need your comment on this. Thanks