Hi Team,

we have some issues in relation with TCAN and crystals and your help would be highly appreciated. We would need your expert team in this case, because it is urgent.

We have problems with not working CAN communication on 1% of the tasted PCBAs. So far, we have assembled more than 20K units. Lately we are also experiencing reclamations the units which went through all the tests OK are coming back not working. We assume that crystal calibration/matching on the PCB is not made properly and therefore we are experiencing these problems.

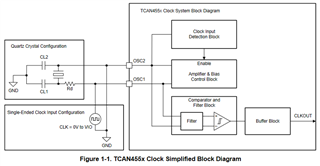

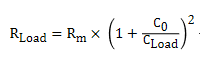

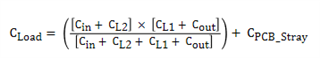

The Crystal HKC2016SX-40MHZ-31303-R4V1 is used for the clock on the TI TCAN4550RGYRQ1 with load capacitors 6pF.

The signal carrier frequency on the CAN bus is not shifted. The problem is that on unstable PCBAs/crystals communication sometimes it is working and then it stops, or it never starts.

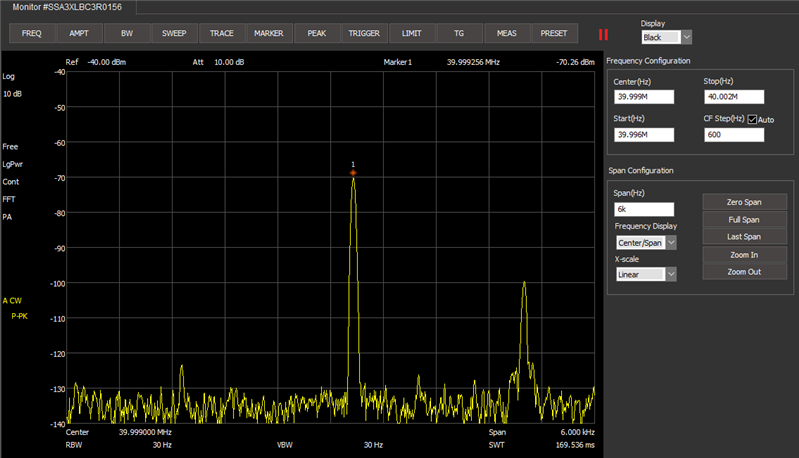

From the measurements of the crystal frequency with spectrum analyzer we don’t see a shift in crystal frequency:

What we have detected is that if we heat or cool down the unstable PCBA the CAN communication starts to operate normally. Or if we touch the load capacitors with the finger the CAN communication starts for a while.

Any help will be appreciated.

Thank you!

Seba