Part Number: SN65DPHY440SS

Hi Teams,

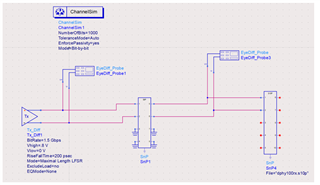

Do we have IBIS model for SN65DPHY440SS? My customer is evaluating SN65DPHY440SS and they want to simulate this part in ADS.

Can you kindly provide this model?

Another question, can we convert S-parameter model to IBIS model?

Tks and BRs

Marsh