Other Parts Discussed in Thread: ALP

<------->ds90ub953

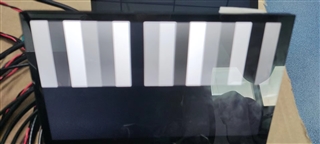

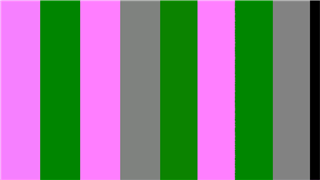

when the configuration of ds90ub953 is in pattern mode and the configuration of the physical data channel of ds90ub954 is 4, the acquired image has black edges.

When the physical data channel of ds90ub954 is 2, the display is normal

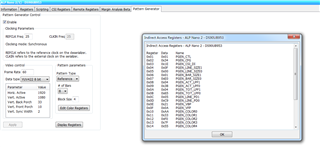

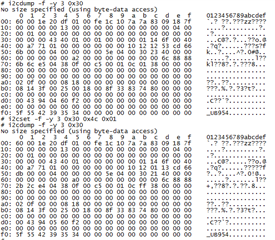

1.Register setting when Mipi physical data channel is 4

{0x33, 0x43}, /* 4 lane */

{0x1F, 0x00}, /* 1.6Gps csi clock per lane */

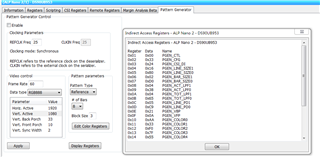

2. Register setting when Mipi physical data channel is 2

{0x33, 0x63}, /* 2 lane */

{0x1F, 0x00}, /* 1.6Gps csi clock per lane */

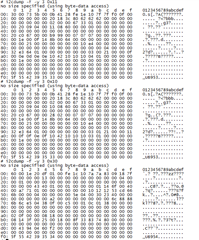

3. The ds90ub953 maintains the following configuration:

{0x01, 0x07},

{0x02, 0x73},

{0x03, 0x5b},

{0x05, 0x0b},

{0xB0, 0x00},

{0xB1, 0x01},

{0xB2, 0x01},

{0xB1, 0x02},

{0xB2, 0x34},

{0xB1, 0x03},

{0xB2, 0x1E},

{0xB1, 0x04},

{0xB2, 0x0F},

{0xB1, 0x05},

{0xB2, 0x00},

{0xB1, 0x06},

{0xB2, 0x01},

{0xB1, 0x07},

{0xB2, 0xE0},

{0xB1, 0x08},

{0xB2, 0x04},

{0xB1, 0x09},

{0xB2, 0x38},

{0xB1, 0x0A},

{0xB2, 0x04},

{0xB1, 0x0B},

{0xB2, 0x65},

{0xB1, 0x0C},

{0xB2, 0x05},

{0xB1, 0x0D},

{0xB2, 0xC9},

{0xB1, 0x0E},

{0xB2, 0x21},

{0xB1, 0x0F},

{0xB2, 0x0A},

{0xB1, 0x10},

{0xB2, 0xAA},

{0xB1, 0x11},

{0xB2, 0x33},

{0xB1, 0x12},

{0xB2, 0xF0},

{0xB1, 0x13},

{0xB2, 0x7F},

{0xB1, 0x14},

{0xB2, 0x55},

{0xB1, 0x15},

{0xB2, 0xCC},

{0xB1, 0x16},

{0xB2, 0x0F},

{0xB1, 0x17},

{0xB2, 0x80},

{0xB1, 0x18},

{0xB2, 0x00},

{0xB1, 0x19},

{0xB2, 0x00},

{0xB1, 0x1A},

{0xB2, 0x00},

{0xB1, 0x1B},

{0xB2, 0x00},

{0xB1, 0x1C},

{0xB2, 0x00},

{0xB1, 0x1D},

{0xB2, 0x00},

{0xB1, 0x1E},

{0xB2, 0x00},