Part Number: DS90UB948-Q1

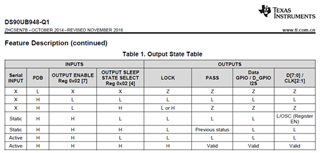

1. The difference between Static and Active

2. What to do to reach the input Active

3. Explain exactly when to lock

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DS90UB948-Q1

1. The difference between Static and Active

2. What to do to reach the input Active

3. Explain exactly when to lock

Hi, Yang,

When PDB is driven HIGH, the CDR PLL begins locking to the serial input and LOCK is tri-state or LOW (depending on the value of the OUTPUT ENABLE setting). After the deserializer completes its lock sequence to the input serial data, the LOCK output is driven HIGH, indicating valid data and clock recovered from the serial input is available on the LVCMOS and LVDS outputs. The state of the outputs is based on the OUTPUT ENABLE and OUTPUT SLEEP STATE SELECT register settings. See register 0x02 in Section 7.7 in the 948 datasheet.

Please check the latest datasheet at TI.com

Regards,

Fadi A.

Hi Yang,

X means do not care, it can be either signal.

Static serial input is referring to the FPD-Link III input not toggling, which would mean that either the line is disconnected or the serializer is powered down.

Active Serial input means a normal video/signal toggling at the input.

Regards,

Fadi A.