Hello,

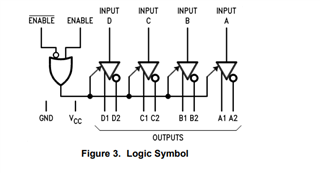

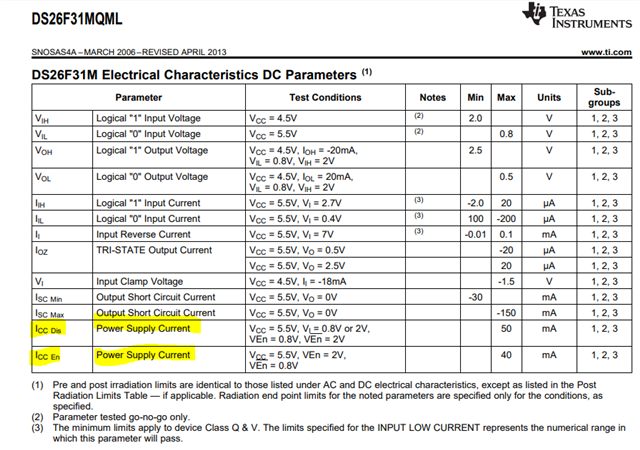

We have seen high current consumption(approximately 30 mA) while Enable'(active low) pin is held High and Enable(active high) pin is held as high. But when Enable' is held low (While Enable pin is still held as High), the current consumption reduces to 19 mA. Could you please explain why current consumption is getting higher in that case?

| Pin | State | Current Consumption(@VCC) |

Enable |

0 | 19 mA |

| Enable | 1 |

| Pin | State | Current Consumption(@VCC) |

Enable |

1 | 30 mA |

| Enable | 1 |

Regards,

Zafer Çalışkan