Part Number: DS90UB954-Q1

Other Parts Discussed in Thread: DS90UB935-Q1, DS90UB953-Q1, ALP

Hi,

I'm working on a image capturing function and the camera is based on the DS90UB953. I'm programming the soc PCBA which having a DS90UB954.

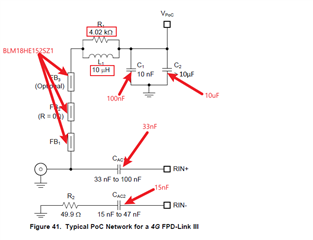

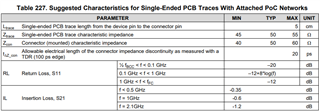

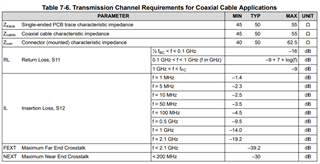

The link between is coax and fpdlink's on the port0 of 954. The POC is stable and confirmed from the oscilloscope.

The camera is from other company and is a black box to me.

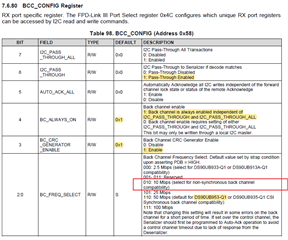

Now the problem is, the same camera can work with one of my project, PROJECT A, through BC_FREQ_SELECT configuration of 110: 50 Mbps (default for DS90UB953-Q1 or DS90UB935-Q1 CSI

Synchronous back channel compatibility).

Another project, PROJECT B, can only work through BC_FREQ_SELECT configuration of 010: 10 Mbps (select for non-synchronous back channel

compatibility). If I use the same 50M configuration, the link can not establish a stable lock status, and the LOCK_STS_CHG is always asserted.

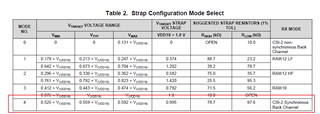

The default 954 MODE pin configuration of both my projects is,

I don't know if the camera is working under synchronous mode or non-synchronous mode, but it seems confusion from the behavior of the 2projects.

Can you help to analyze what's the situation between the 2projects from a serdes perspective? It's really confused me.

Thank you!