Other Parts Discussed in Thread: LMK04803

Hello support team,

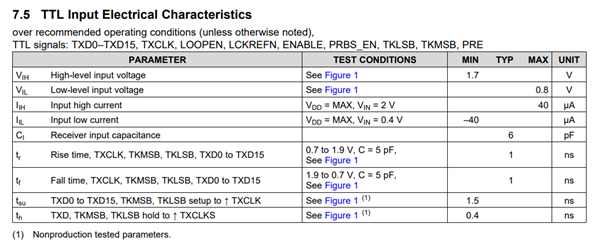

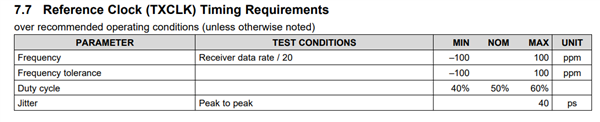

We are planning to use the Clock synthesizer(LMK series) for the TXCLK provision of 110 MHz to TLK2711 SERDES IC. As per datasheet and calculations, found out that the required RMS jitter performance is < 450 femto sec. But my question is about the integrated BW. How to select the Integrated BW criteria on which jitter performance needs to be verified? Can you please guide on the same?

As all LMK series clock synthesizer has given their characteristics on jitter is 111 femto sec(approx) with the integrated BW of 12 KHz to 20 MHz.