Part Number: SN65LVDT2

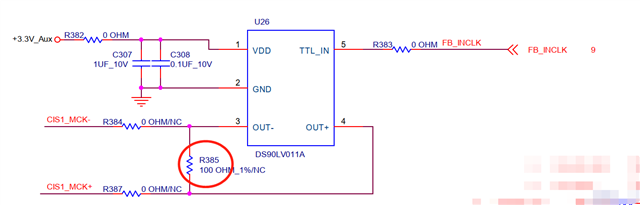

Other Parts Discussed in Thread: DS90LV011A

Hello TI experts:

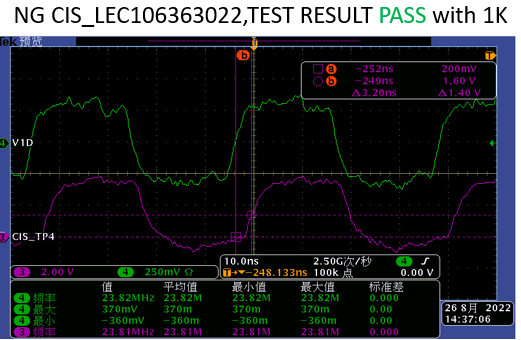

the above is SN65LVDT2 waveform, TP4 is Output PIN,which alway keep Low level, normally TP4 should be output normal clock;

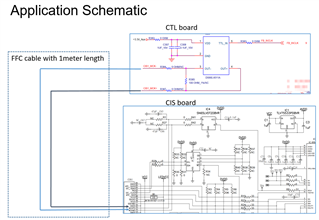

the transmiter IC is DS90LV011A from controller board,after add 1K ohm resistor near to DS90LV011A chip, we can get normal output from SN65LVDT2 as below.

Can someone take a look tell me what is different between two waveform picture, i do not know which parameter on NG CIS can not meet SN65LVDT2 spec.