Part Number: DS250DF230

Hi,

The customer wants to combine an MSP430F5419AIPZR (master) with a DS250DF230ZLSR (slave) for I2C communication.

From the thread below, we can read Clock low period (min) = 1.3 us (400kHz class).

1. Is the DS250DF230 ”clock low period" rounded up to 1.3us?

2. Can they use the DS250DF230 "clock low period" at 1.28us?

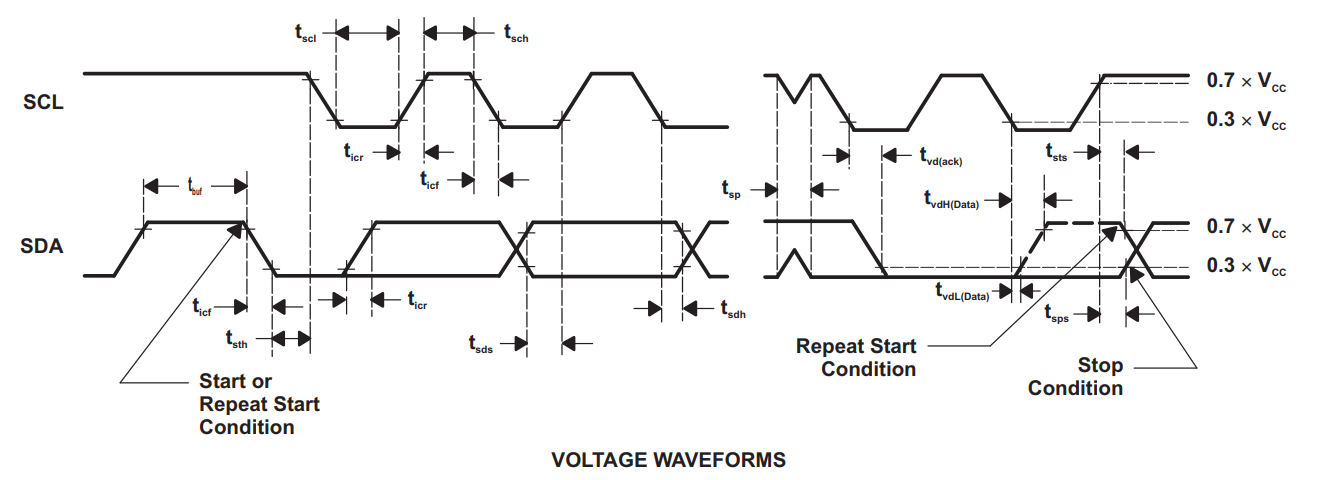

3. Is there a timing chart with tlow, tSU_DAT, etc.?

Best Regards,

Nishie