Part Number: TCAN4550

Hi,

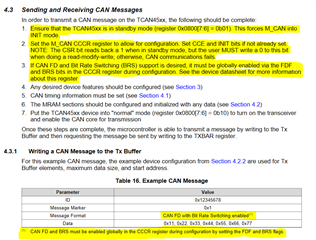

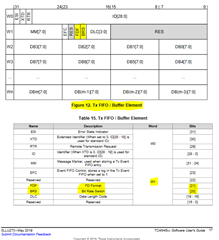

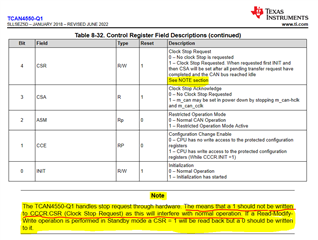

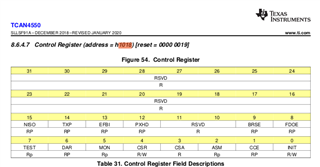

I am testing CANFD. Sending 64 data bytes at regular speed is blocking the CAN bus. I want to turn on bit rate switching by writing 9th bit of the register h1018. But 9th bit is READ WRITE PROTECTED type. So I am not able to write this bit to high for enabling bit rate switching for transmission enabled. What is the solution for this?

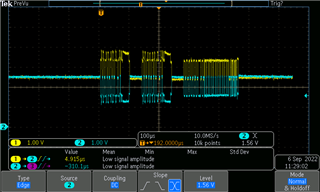

Below is the snapshot for the same.

Regards,

Akshay