Hi Team,

My customer needs clarifications regarding the two ICs, please see details below.

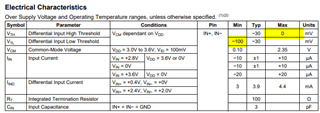

I am looking for a replacement for the SN65LVDT2DBV LVDS receiver IC in the SOT23-5 package with the internal 100 Ohm resistor. The DS90LT012AQMFX/NOPB is a possible candidate. So in comparing the two receiver IC's I got stuck when looking at the input threshold specifications.

The original part (SN65LVDT2DBV) has a spec of +/- 100 mv. This seemed simple enough to understand. But the possible new part (DS90LT012AQMFX/NOPB) input threshold spec said "0 to -30 mv". The following paragraph from the spec sheet (Page 5) seemed to indicate that this alternate specification was a performance enhancement - but I'm afraid I don't understand how that works.

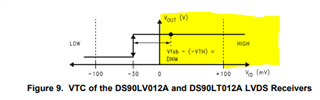

"THRESHOLD The LVDS Standard (ANSI/TIA/EIA-644-A) specifies a maximum threshold of ±100mV for the LVDS receiver. The DS90LT012AQ supports an enhanced threshold region of −100mV to 0V. This is useful for fail-safe biasing. The threshold region is shown in the Voltage Transfer Curve (VTC) in Figure 6. The typical DS90LT012AQ LVDS receiver switches at about −30mV. Note that with VID = 0V, the output will be in a HIGH state. With an external fail-safe bias of +25mV applied, the typical differential noise margin is now the difference from the switch point to the bias point. In the example below, this would be 55mV of Differential Noise Margin (+25mV − (−30mV)). With the enhanced threshold region of −100mV to 0V, this small external fail-safe biasing of +25mV (with respect to 0V) gives a DNM of a comfortable 55mV. With the standard threshold region of ±100mV, the external fail-safe biasing would need to be +25mV with respect to +100mV or +125mV, giving a DNM of 155mV which is stronger fail-safe biasing than is necessary for the DS90LT012AQ. If more DNM is required, then a stronger fail-safe bias point can be set by changing resistor values."

My concern that is if there is a certain amount of noise in my system that is rejected by the +/-100mv threshold of the old part, could it then be accidentally registered as data in the smaller and negative biased window of (0 to -30 mv) in the new part?

Thank you.

Regards,

May