Part Number: TIOL111

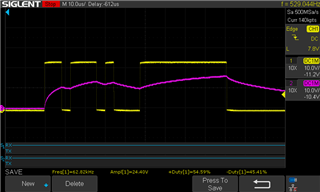

Other Parts Discussed in Thread: , , TIOL112, LM5160

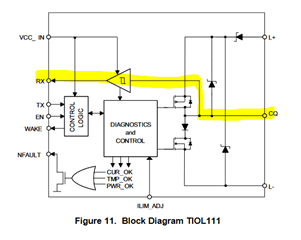

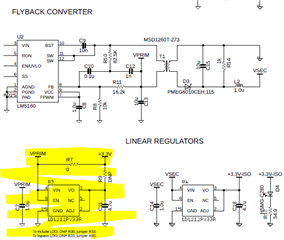

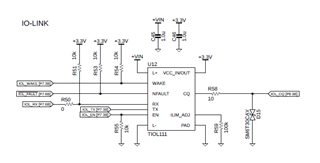

We are having issues where the transceiver is behaving strangely over time. Below is the relevant schematic.

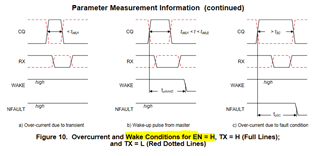

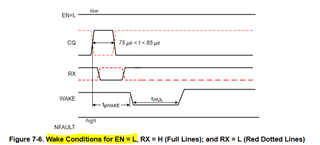

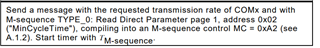

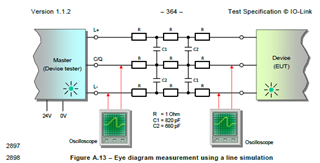

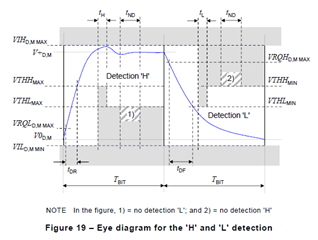

Our device is not responding to the IOLink master wake-up request - we should be using the 230.3kBaud COM3, but we are trying to determine why our device is not responding. Because we never respond the master repeatedly polls at each of the three baud rate options. Probing the data line into the transceiver compared to the data pushed out the RX pin of the transceiver, shows the expected output at slower two speeds:

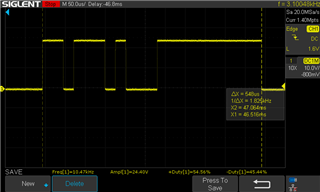

COM1, input (IOL CQ data line) to TIOL111:

COM1, output (RX line from transceiver to microcontroller):

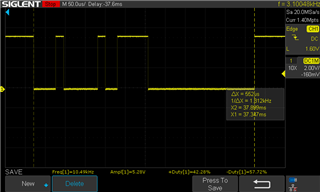

COM2, input to TIO111:

COM2, output from TIOL111:

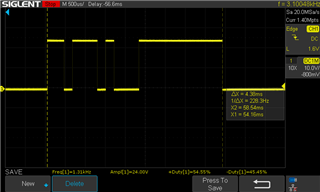

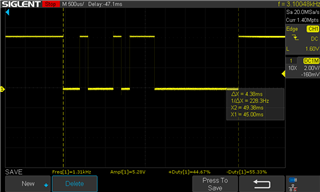

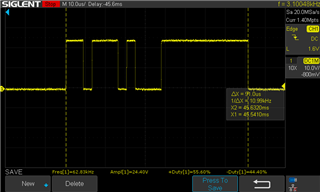

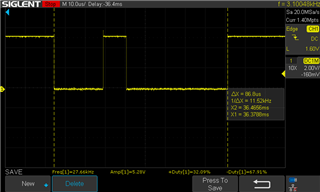

However, at COM3, the transceiver RX output does not match the input that it is receiving:

COM3, input to TIOL111:

COM3, output from TIOL111:

Are there any known issues with the device at COM3, or issues to be aware of, or any similar problems that have been experienced? This has developed recently and we have a very short deadline to resolve the issues for our customer.

Thank you.