Dear Team,

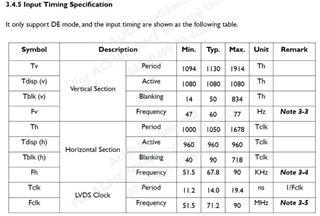

The LCM panel support the following input timing.

What is the input timing of the sn65dsi84 corresponding to the following LVDS timings?

I have some other questions:

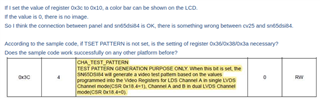

1.After register setting, the value of register 0xE5 is 0x1, is it OK?

2.How can I check the video data stream sent to sn65dsi84 is OK?

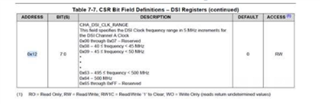

3.In chapter7.6 of sn65dsi84 spec, description of register 0x0D, does it mean mipi PHY clock must be enabled before PLL is enabled?

4.I used Oscilloscope to measure the input clock and mipi data for LCD, but the result was not that good to see, how can I measure it better?

Platform: Ambarella CV25 SoC

System: Linux

Bridge IC: SN65DSI84

Many Thanks,

Jimmy