Part Number: DP83867IS

Other Parts Discussed in Thread: TXS0102,

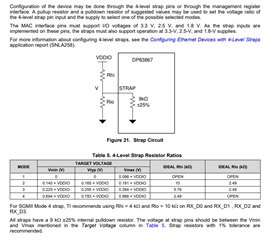

Hi,

I am using the TI DP83867 phy device in my design.

The MDIO interface from my SOC is interfaced to the TI DP83867 phy with the TI TXS0102 device in between.

On MDC at the Phy device (after the TXS0102), we observe a drooping waveform after the MDC clock goes from Low to High which we understand is due to the internal pull down resistor on the MDC pin in the DP83867 device.

I have a few queries with respect to this interfacing:

1. What is the spec for the internal pull down resistor on MDC?

- This is to understand to what level the drooping waveform will drop.

2. Currently I am assuming that the drooping waveform after the MDC clock goes from Low to High is not a concern because the MDIO data is sampled on the rising edge of MDC.

For reference I have attached the clock waveform "TXS0102_MDC_A_Output_DroopingWaveform.jpg".

- Kindly advise if this waveform could cause problems/ violate any DP83867 MDC input spec.

Thanks

Louis