Hello,

I had some questions a few weeks ago in this forum theme:

I did some changes in my schematic and now I have a new issue.

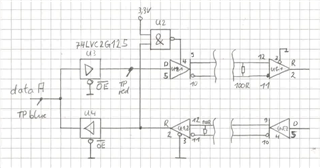

I want to give a short introduction to my schematic:

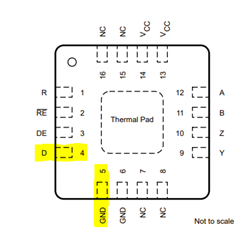

A logical signal will be sent from “data A2 via the bus driver “74LVC2G125” (U3). Then the signal should go into the D input from a SN65MLVD203B (U1.1). The chip U1 is connected to a corresponding device U5 with the same logic constellation as U1. (that’s why I did not draw the logical side from U5). U2 is therefore to allow only transmitting signals via the D input from U1.1 when nothing will be received via the R line from U1.2. The bus drive U4 serves as a diode so that the signal can only be transmitted in one direction.

My problem is the R line input from U1. First, I had the schematic without U3, but it looks for me that the D line pulls down any kind of logical signals. To be sure I added the U3 chip.

I made a screenshot from my oscilloscope:

On the blue channel a logical signal from a microcontroller can see (3.3V). The red signal is the output from U3 and so also the input level from the D line. For me it is not clear why the logical signal is so much lower than the data A signal. Before I add the bus driver U3 I used a frequency generator and I have to increase the frequency output voltage up to 4.5 volts to get a 3.3V input signal on the D line.

So, my thought is that the D line from U1 pulls the signal down to 0V.

Does someone have an idea why this could be? Is my SN65MLVD203B maybe damaged? But therefore, I changed the chip with a bread new device and then I get the same result.

Best regards,

Marcel