Other Parts Discussed in Thread: ALP

Hi Team,

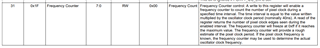

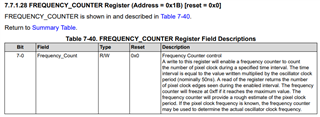

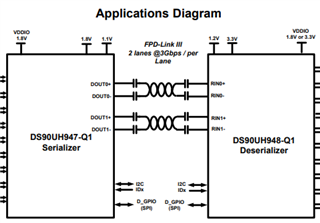

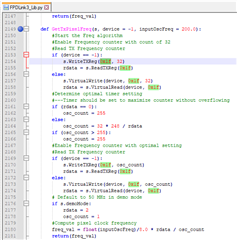

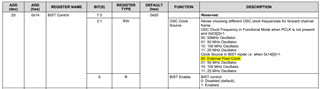

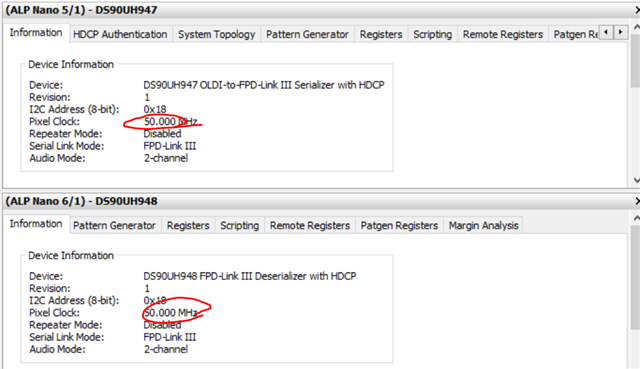

As you know, there is PCLK information in ALP Information page. I want to know if there is any register can indicate the PCLK of 947 using and 948 using.

In addition, I want to check the PCLK on 947 and 948.

For 947 PCLK, does it mean that the PCLK that 947 received?

For 948 PCLK, does it mean that the PCLK that 948 sent?

Regards,

Roy