Other Parts Discussed in Thread: TLK10232,

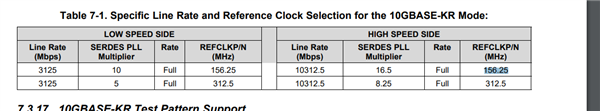

Ref clock = 156.25MHz

- LS side: connected to 4 channels XAUI

- HS side is connected to a Marvell switch in 10G-KR

We can read and write registers in the TLK (reading correct default values, and can change them).

We work with AN disable.

We have tried also changing the HS_ENPLL bit in HS_SERDES_CONTROL_1 from default 0 to 1.

Problem: None of the changing registers, i.e. CHANNEL_STATUS_1 (register: 0x000F) (default: 0x0000) (device address: 0x1E), or HS_ERROR_COUNTER or LS_LN0_ERROR_COUNTER, are showing any change from their default values. Looks like that except from reading and writing registers the device is not functioning, and links are not coming UP.

We have checked the following signals on our board:

- REFCLK0 = 156Mhz as shown in the attached plot.

- MODE_SEL = 0V

- ST = 0V

- PRBSEN = 0V

- TESTEN = 0V

- PDTRXA_N = 1.5V

Any idea what might be the problem?

Thx

Omri