Regarding ti's 960 and 964, I would like to ask the spec that the minimum rising edge time of Vdd and VDDIO should be 200ns. If this index is not met, what will be the negative impact?

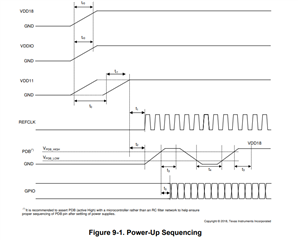

There is another problem, that is, regarding the power on timing of 960 and 964, I don't know if there is a clear sequence requirement. Look at the spec, 964 says that the minimum time of power on t0, T2 and T4 from vdd11 to VDD / VDDIO is 0ms, and the legend indicates the time from the power supply stabilization; However, it is written in 960 that the minimum time from VDD / VDDIO to vdd11 is 0ms, but the legend indicates the time from 10% of the power supply