Other Parts Discussed in Thread: TFP401,

Hi Experts,

Good day.

The TI product of interest is the TFP401APZP.

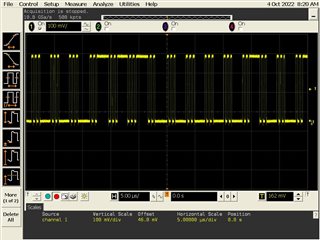

The specification states that if the mode settings are DFO: Lo, PIXS: Lo, OCK_INV: Lo, ODCK will be free-running.

I made the same settings, but even if I supplied power to the TFP401APZP, I could not confirm the movement of the waveform from ODCK.

Even if the clock is not input to the RxC signal on pins 93 and 94, an indeterminate waveform should be output from ODCK, but it is not output.

Is this a product defect? please advise.

Keep safe.

Regards,

Josel