Other Parts Discussed in Thread: DS90LV047A, , SN65LVDS31, DS90LV031A

Hi

we have a bus of 10 signals that we have to translate from CMOS_1V8 to LVDS.

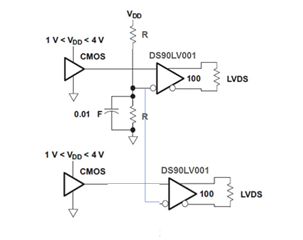

we understand that we need to bias the "-" input to 0.9V by using resistor network (resistor value: 1V8 / 600uA = 3K)

because we have up to 10 buffers, we would like to eliminate some of these resistor networks.

Using 1 network for a group of 4 devices for example.

In some situation, the buffer will not be powered and the 1V8 on resistor network will be present

if we have 10 resistor networks, the total current @ 1V8 will be around (1.8 - 0.3) / 3000 * 10 = 5ma + the leakage current in the input pins

we can reduce it by reducing the QTY of network

any recommendation about this proposed architecture ?

We assume that the leakage current in the input pin will not be so high at <0.9V, any estimation?

thanks

Yves