Part Number: DP83640

Other Parts Discussed in Thread: AM5728,

Hi,

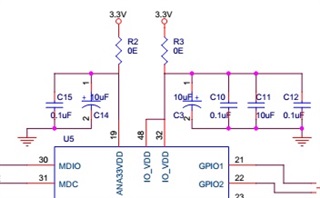

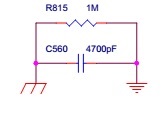

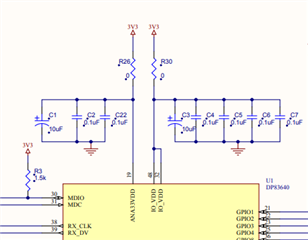

We are in the development stage of AM5728 based Bay Control Unit, for that we have to use DP83640 IEEE 1588 PTP ethernet PHY transceiver.

We have to configure DP83640 in the Master-Slave Mode(with Optical/RJ45 mode) .Now we designed a schematic by referring DP83640T-EVK design files obtained from below link https://www.ti.com/tool/DP83640T-EVK

Here we are attaching the schematic diagram of our DP83640 Master-Slave Mode.

Please help review the schematic diagram